Съдържание:

- Стъпка 1: Работа на потребителя с цифров секвенсор

- Стъпка 2: Технически подробности

- Стъпка 3: Технически подробности

- Стъпка 4: 7-сегментен часовник

- Стъпка 5: Делител на часовника за минута

- Стъпка 6: Разделяне на часовника

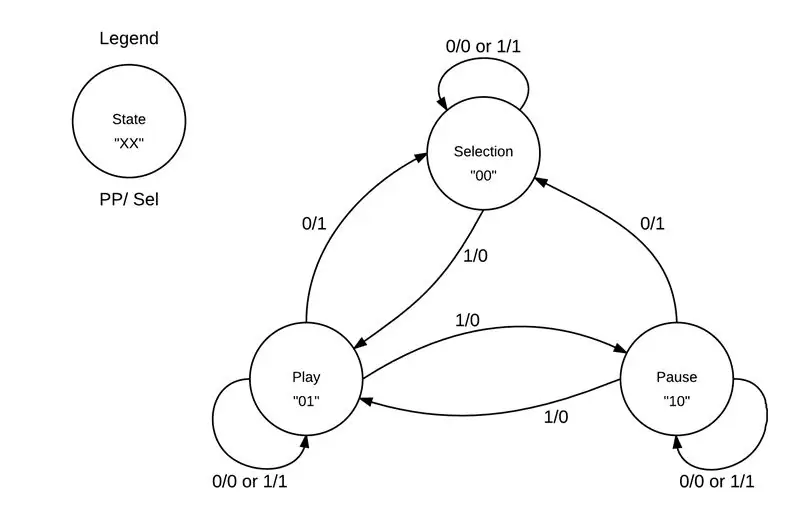

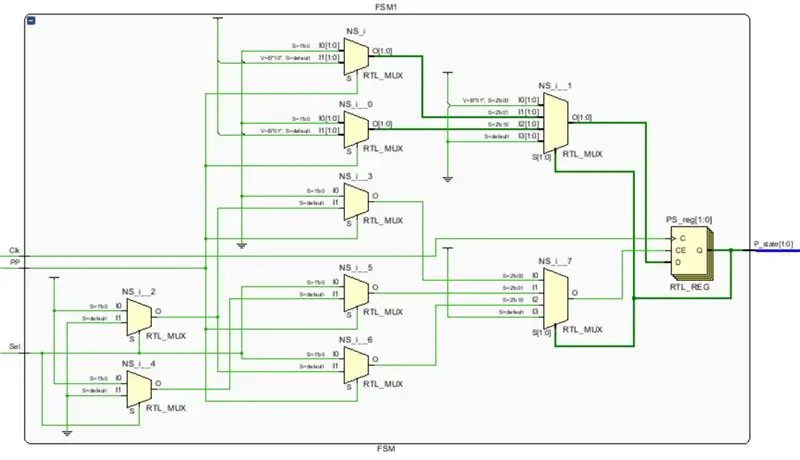

- Стъпка 7: Възпроизвеждане/Пауза/Избор на машина на състоянието

- Стъпка 8: Възпроизвеждане/Пауза/Избор на машина на състоянието

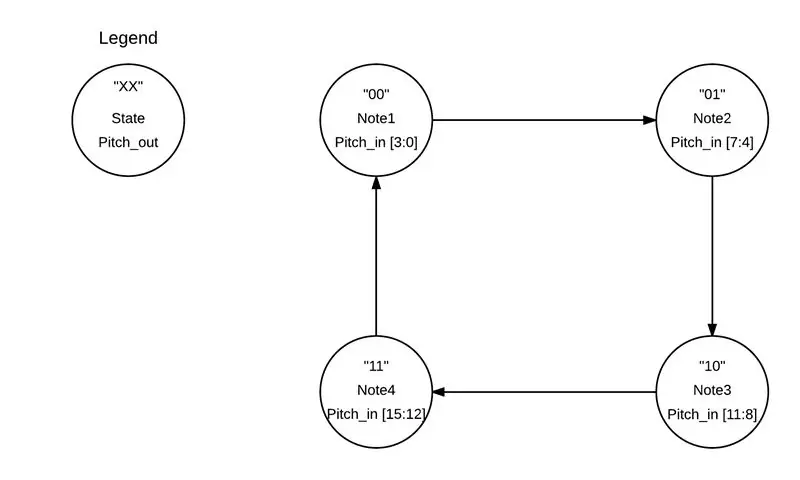

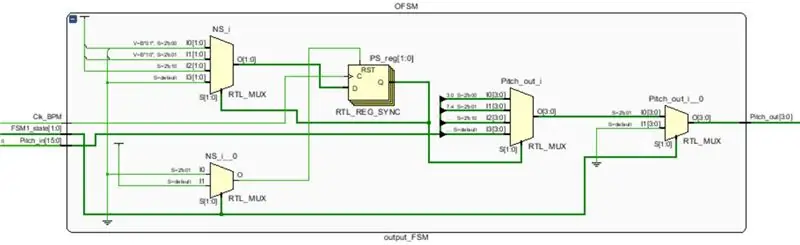

- Стъпка 9: Изходен FSM

- Стъпка 10: Изходен FSM

- Стъпка 11: Задайте бележка

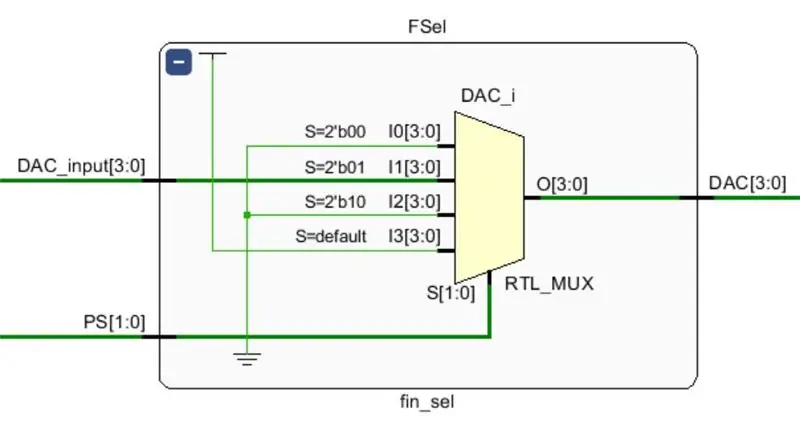

- Стъпка 12: Избор на изход

- Стъпка 13: Square Wave Gen

- Стъпка 14: 7-сегментен дисплей

- Стъпка 15: Окончателен избор

- Стъпка 16: Външни устройства: DAC

- Стъпка 17: Външни устройства: Високоговорител

- Стъпка 18: Видео демонстрация

- Стъпка 19: VHDL код

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 07:54.

- Последно модифициран 2025-01-23 14:36.

CPE 133, Cal Poly San Luis Obispo

Създатели на проекта: Джейсън Джонстън и Бьорн Нелсън

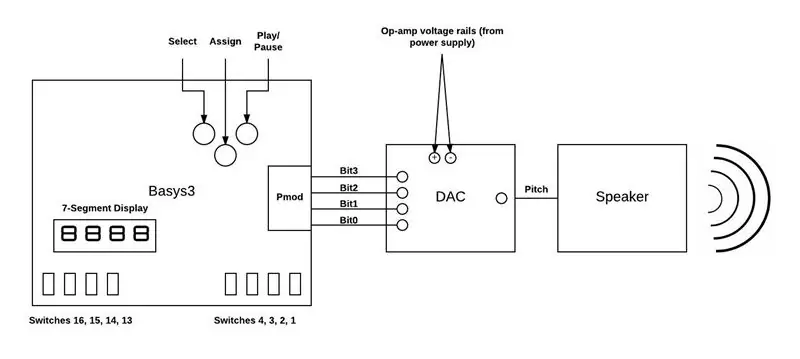

В съвременната музикална индустрия един от най -често използваните „инструменти“е цифровият синтезатор. Всеки музикален жанр, от хип-хоп до поп и дори кънтри, използва дигитален синтезатор в студиото, за да създаде ритъмите и звуците, от които се нуждаят, за да оживят музиката си. В този урок ще създадем много прост синтезатор с платката Basys 3 FPGA.

Синтезаторът ще може да свири четири избрани четвъртинки с постоянен брой удари в минута. Потребителите ще използват превключвателите, за да присвоят всяка четвърт нота на музикална висота. За този проект използваме 4-битов цифров към аналогов преобразувател (DAC), за да вземем изхода от платката и да го преобразуваме в аналогов сигнал. След това изходът от DAC ще се подава към стандартен компютърен високоговорител, създавайки нашата музика. Възможни са шестнадесет дискретни височини. Ще ограничим нашия синтезатор до една октава от 12 ноти, които попадат между средата C (261.6 Hz) и B4 (493.9 Hz). Потребителят също така ще има възможност да зададе няколко бележки едновременно, както и да назначи почивка чрез натискане на присвояване, без никой от превключвателите за височина да е изместен нагоре. Тъй като всяка нота е избрана и свирена, нотата с буквата се показва на 7-сегментния дисплей. Ще използваме и три от бутоните на дъската, един за възпроизвеждане и пауза на музиката, един за нулиране на синтезатора и поставянето му в режим „избор”, а третият за присвояване на всяка нота на височина, докато е в режим на избор.

След като потребителят е доволен от избора си на ноти и след натискане на бутона за възпроизвеждане, синтезаторът ще възпроизвежда всяка нота последователно многократно, докато потребителят не натисне пауза или изберете.

Ето списък на необходимото оборудване:

- Vivado (или всяко друго VHDL работно пространство)

- Basys 3 или подобна FPGA платка

- Цифро-аналогов преобразувател (мин. 4-бита)

- Високоговорител с жак за слушалки

- Кабелни проводници

Стъпка 1: Работа на потребителя с цифров секвенсор

Следните стъпки са за работа с цифровия секвенсор. Цифровият секвенсор поддържа възпроизвеждането на 12 различни височини (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), които варират от 261,6 Hz до 493,9 Hz.

1. Натиснете левия бутон, за да поставите дъската в режим на избор. Когато сте в този режим, най -лявите 4 превключвателя (превключватели от 13 до 16) ще се използват за съхраняване на отделна стойност на височината.

2. За да направите избор, включете един от левите превключватели и след това използвайте най -десните 4 превключвателя (превключватели от 1 до 4), за да изберете желаната височина. Височината, свързана с конкретна комбинация от десни превключватели, ще се показва на седемсегментния дисплей и дисплеят ще се актуализира до новата свързана височина, когато десните превключватели бъдат изместени към нова комбинация. Почивката може да бъде назначена, като никога не се присвоява височина на един от левите превключватели или като се присвоява на нотата височина, показана като 0 на дисплея. След като желаната височина е намерена и се показва на дисплея, натиснете долния бутон за задаване, за да присвоите тази конкретна височина на нотата.

3. Повторете стъпка 2 за трите останали ноти, като включите всеки от останалите леви превключватели поотделно, изберете съответната височина с десните превключватели и натиснете долния бутон, за да зададете височина на нотата. Няколко ноти могат да бъдат присвоени на една и съща височина чрез преместване на повече от един от левите превключватели нагоре едновременно.

4. След като всички ноти са зададени, цифровият секвенсор е готов за свирене. За да пуснете нотите на високоговорителя, просто натиснете десния бутон за възпроизвеждане/пауза, за да започнете да възпроизвеждате музиката. Редът на последователността на възпроизвеждане отразява височините, свързани с левите превключватели, отляво надясно. Нотите ще се изпълняват с определен брой удари в минута, в ред 1, 2, 3, 4, 1, 2…. Дисплеят ще покаже нотата, която се изпълнява в момента, когато високоговорителите възпроизвеждат музиката. За да спрете възпроизвеждането на музика, просто натиснете десния бутон и тогава музиката ще спре да се възпроизвежда и на дисплея ще се покаже символ за пауза. Повторното натискане на десния бутон ще възобнови възпроизвеждането.

Стъпка 2: Технически подробности

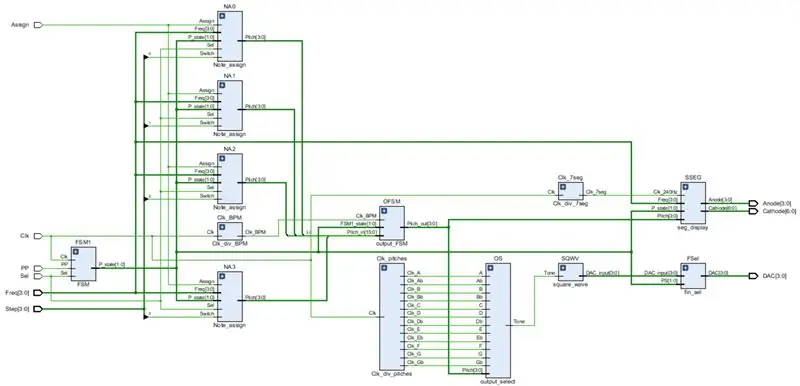

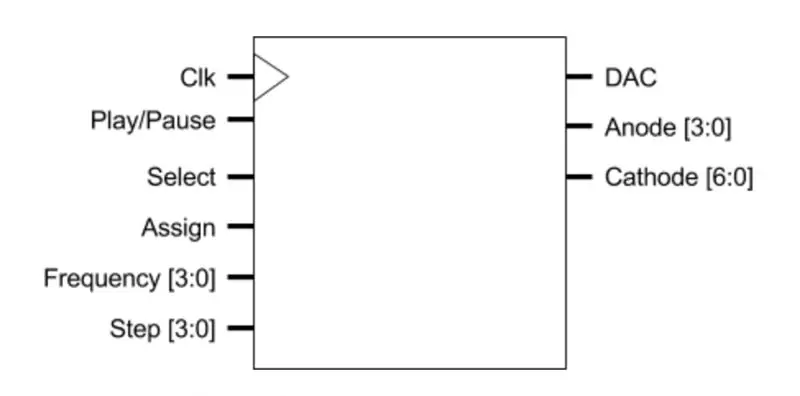

Нашият синтезатор използва много различни цифрови компоненти. Включени са машини с крайни състояния, регистри, мултиплекси, часовници и други. За да изградим нашия синтезатор, използвахме 10 уникални модулни файла. Вместо да правим всеки модул компонент, ние разбихме модулните файлове по функции. В резултат на това повечето модули са повече от един компонент. Обърнете внимание, че изображението по -горе показва всеки блок, свързан заедно в нашия топ дизайн.

Ще обсъдим всеки модул, като опишем входовете и изходите, разбивайки неговите компоненти и обяснявайки неговата цел в цялостния дизайн. В долната част на инструкцията е включен ZIP файл, който съдържа всеки VHDL код файл, използван в проекта.

Входове

- Clk (собствен часовник сигнал)

- PP (възпроизвеждане/пауза)

- Sel (поставете синтезатора в режим на избор)

- Присвояване (задаване на стъпка към терена)

- Стъпка (позиционните бележки)

- Честота (превключвателите създават желаната височина)

Изходи

- Анод (7-сегментни аноди)

- Катод (7-сегментни катоди)

- DAC (4-битов управляващ DAC)

Стъпка 3: Технически подробности

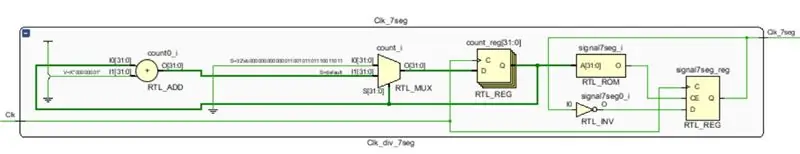

Стъпка 4: 7-сегментен часовник

Нашият синтезатор използва три часовникови разделители, всички произвеждащи сигнали, които служат за различна цел в нашия проект. Делител на часовник приема естествен часовник сигнал и произвежда променен сигнал, който има честота, която е по -малка от оригиналния часовник сигнал. Местният часовник на Basys 3 е 100 MHz. Това е честотата, която нашите часовници използват. Ако използвате различна FPGA платка с различна родна тактова честота, може да се наложи да промените кода.

7-сегментният часовник разделител произвежда сигнал, който задвижва файла seg_display. Ще обясним как работи този файл по -подробно, когато стигнем до неговия раздел. По същество този часовник разделител произвежда 240 Hz сигнал, който ще се използва за превключване между аноди и катоди на дисплея. Сигналът е 240 Hz, тъй като честотата, с която човешкото око не може да разпознае липсата на светлина, е 60 Hz. Използваме две цифри, така че удвоявайки тази честота, всяка цифра ще се колебае при 60 Hz. След това го удвояваме, за да получим 240 Hz, защото системата се променя само когато сигналът се повиши, а не когато падне.

За да се постигне това, разделителят приема собствения 100 MHz сигнал и отчита всеки нарастващ ръб. Когато броячът достигне 416667, изходът ще премине от ниско към високо или обратно.

Входове

Clk (собствен часовник сигнал)

Изходи

Clk_7seg (към seg_display)

Компоненти

- D регистър

- MUX

- Инвертор

- Суматор

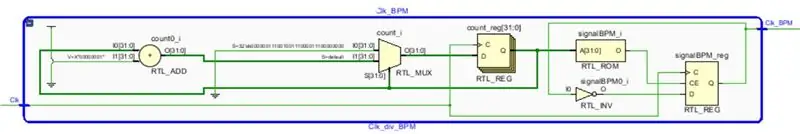

Стъпка 5: Делител на часовника за минута

Часовникът BPM работи по подобен начин. Този разделител произвежда тактовата честота, която задвижва превключването между четирите стъпки при извеждане на тонове в състояние на възпроизвеждане. Решихме да превключваме между бележки на 100 BPM. При 100 BPM всяка нота ще се свири за 3/5 от секундата. Полученият сигнал ще има честота 1,67 Hz.

За да произведем сигнал с тази честота, отново използвахме система за броене, но този път броят беше 60 милиона. Всеки път, когато броячът достигне 60 милиона, изходният сигнал ще превключи високо или ниско.

Входове

Clk (родна тактова честота)

Изходи

Clk_BPM (към изход_FSM)

Компоненти

- D регистър

- MUX

- Инвертор

- Суматор

Стъпка 6: Разделяне на часовника

Разделителят на часовника Pitches е най -големият от нашите часовници. Този разделител извежда 12 различни сигнала, съответстващи на 12 -те различни ноти, които нашият синтезатор може да свири. Използвайки основни познания по музикална теория, стигнахме до извода, че бит или шина може да се колебае със скорост, която съответства на честотата на музикалните ноти. За да видите честотите, които използвахме, погледнете тук. Използвахме четвъртата октава на терена.

Тук се използва същата система за броене. За конкретните стойности, към които сме броили, вижте файла с надпис Clk_div_pitches.

Входове

Clk (родна тактова честота)

Изходи

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (за изход_избор)

Компоненти

- D регистър

- MUX

- Инвертор

- Суматор

Стъпка 7: Възпроизвеждане/Пауза/Избор на машина на състоянието

В нашия проект има две машини с крайно състояние (FSM). FSM е логическо устройство, което може да съществува само в едно състояние от ограничено количество състояния. Използвайки FSM, цифрова верига може да премине в ново състояние въз основа на комбинация от входове. Използвайки логика на входа, състоянието на FSM ще се промени, когато има нарастващ ръб на часовника. От състоянието и входовете във веригата можете да създадете изходна логика, която дава изходи, които съществуват само ако FSM е в определено състояние.

PPS състоянието машина е първият FSM в нашата верига. В този FSM има три състояния; Режим на възпроизвеждане, пауза и избор. За да се придвижваме през различните състояния, използвахме бутоните PP и Selection. Вижте диаграмата на състоянието по -горе, за да видите как се случват преходи между състояния. Направихме този FSM преход на нарастващия ръб на родния часовник от 100 MHz, така че да бъде невъзможно машината да не премине при натискане на един от бутоните, дори за много кратък период от време. Настоящото състояние (P_state) е единственият изход от този модул.

Входове

- Clk (родна тактова честота)

- Sel (ляв бутон)

- PP (десен бутон)

Изходи

P_state (сегашно състояние, към output_FSM, note_ assignment, seg_dsiplay, final_select)

Компоненти

- MUX

- D регистър

Стъпка 8: Възпроизвеждане/Пауза/Избор на машина на състоянието

Стъпка 9: Изходен FSM

Това е вторият FSM, споменат в предишния раздел. Този FSM изпълнява различна функция от другата, но основата за тази по същество е същата.

Изходният FSM работи само ако настоящото състояние от първия FSM е "01" (състояние на възпроизвеждане). По същество това е активирането на модула. Ако състоянието е "01", тогава FSM ще превключва между състояния по нарастващия ръб на тактовия сигнал на BPM. Правим това, защото output_FSM контролира кой двоичен номер за избраната стъпка да бъде изпратен до модулите output_select и seg_display. FSM има 16-битов вход, идващ от модула за присвояване на бележки, който ще бъде разгледан по-нататък. В състояние "00" за output_FSM, модулът ще изведе "xxxx" за първата присвоена нота. След това в "01" той ще изведе "yyyy" за втората нота и така нататък за всяка нота, преди да се върне обратно към първата нота. Вижте диаграмата на състоянието по -горе.

Този FSM се различава от първия, тъй като няма входна логика за управление на превключването между състояния. Вместо това, FSM ще работи само когато състоянието от първия FSM е "01", а след това този FSM ще премине между състояния само по нарастващия ръб на тактовия сигнал. Друга разлика е, че този модул има изходна логика, което означава, че не извежда текущото състояние, а извежда двоичното число за височината в това състояние.

Входове

- Clk_BPM (BPM тактов сигнал от часовника)

- FSM1_state (PS от PPS FSM)

- Pitch_in (терени от note_ assign)

Изходи

Pitch_out (една стъпка наведнъж, за output_select и seg_display)

Компоненти

- MUX

- D регистър

Стъпка 10: Изходен FSM

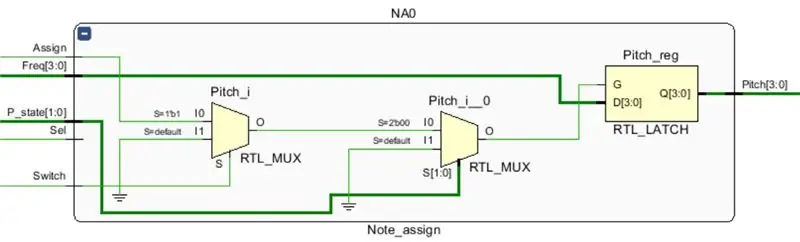

Стъпка 11: Задайте бележка

Модулът за присвояване на бележка е отговорен за действителното присвояване на височина на позиционната бележка или стъпка. Този модул всъщност е доста прост. Първо проверява дали веригата е в състояние на "избор" и дали стъпаловиден превключвател (вляво) е висок. Ако това е вярно и бутонът за присвояване е натиснат, изходът на модула ще бъде равен на двоичното число, представено от честотните превключватели (вдясно).

Първоначално се бяхме опитали да направим модул, който всъщност да запише един от сигналите на часовника на височината на изхода, но изпитахме проблеми с промяната на изхода, за да следва сигналите на входящия часовник. Това е единственият модул, използван повече от веднъж в окончателния дизайн. Всяка стъпка има свързан с него модул note_assign и поради това всеки екземпляр на модула получава по един бит от шината Step.

Входове

- P_state (сегашно състояние от PPS FSM)

- Sel (ляв бутон)

- Превключвател (превключвател с една стъпка)

- Честота (крайни десни превключватели за височина)

- Присвояване (долен бутон, възлага бележка)

Изходи

Pitch (двоично число, към output_FSM)

Компоненти

- MUX

- D повторно регистриране

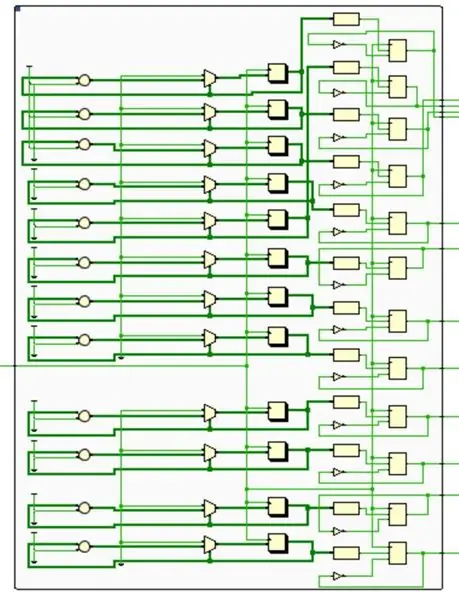

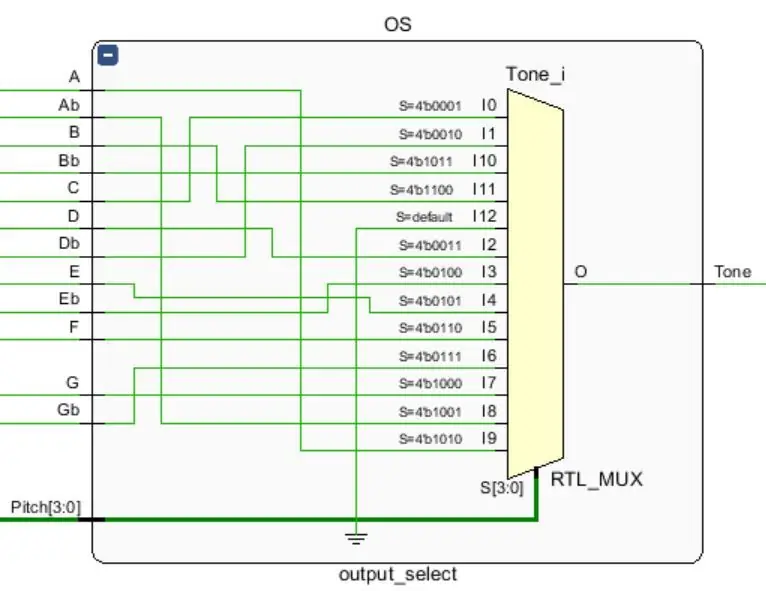

Стъпка 12: Избор на изход

Изборът на изход е отговорен за вземането на двоичното число за височина и свързването му към съответния часовник сигнал. Въпреки размера си, това също е сравнително прост модул. Output_select е по същество двоичен декодер, декодиращ двоичното число за височина до определен тактов сигнал. Всъщност присвояването на изхода на тактова честота работи по -добре тук в сравнение с модула note_assign, защото всичко, което този модул трябваше да направи, беше да MUX часовните сигнали с двоично число, представляващо контролния вход.

Извиняваме се за странното маршрутизиране, Vivado организира сигналите за височина по азбучен ред за файла clk_div_pitches, но за този файл ги организира по възходящ двоичен номер, което води до различен ред на височините. Също така имайте предвид, че ако двоичното число от output_FSM е "0000" или нещо по -голямо от "1100", тогава MUX изпраща чрез плосък сигнал "0".

Вход

- Pitch (от output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (часовникови сигнали)

Изход

Тон (единичен бит, който съответства на избрания часовник сигнал, до квадратна_вълна)

Компоненти

MUX

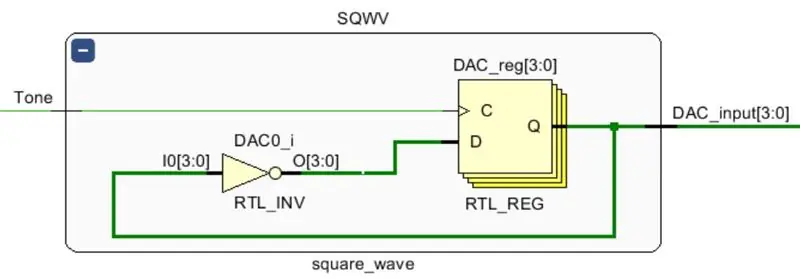

Стъпка 13: Square Wave Gen

Модул square_wave е генераторът за квадратна вълна, която се извежда от платката към DAC. Използвайки тоналния сигнал от предишния файл, тази квадратна вълна инвертира 4 -битовото число между "0000" и "1111" по нарастващия ръб на тона. Тонът е специфична честота на тона, така че square_wave произвежда вълна с различна честота, когато output_FSM преминава в друго състояние. 4-битовият изход от този модул отива към модула fin_sel, където логиката диктува дали тази шина ще бъде изведена въз основа на състоянието от PPS FSM.

Алтернатива на този генератор на квадратни вълни е генерирането на синусоида. Въпреки че това най -вероятно ще доведе до по -добър краен тон, той е значително по -труден за изпълнение, затова решихме просто да генерираме квадратна вълна.

Входове

Тон (осцилиращ бит от output_select)

Изходи

DAC_input (осцилираща 4-битова шина, която се променя при същата честота на тона)

Компоненти

- Инвертор

- D регистър

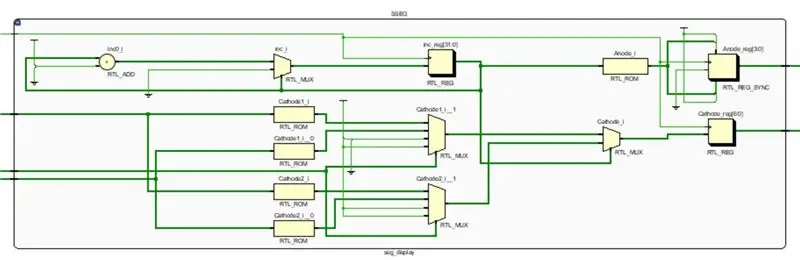

Стъпка 14: 7-сегментен дисплей

Модулът seg_display контролира 7-сегментния дисплей на нашата базова платка. В рамките на модула се случват два процеса. Първият процес декодира Freq, когато е в състояние "избор" или Pitch, когато е в режим "възпроизвеждане". В режим "пауза" модулът декодира, за да покаже символа за пауза. Разглеждайки VHDL кода, можете да видите, че двоичният декодер всъщност декодира входа в два различни сигнала, катод1 и катод2. Катод 1 представлява буквата, съответстваща на височината, която трябва да се покаже, а катод 2 представлява плоския символ (б), ако има такъв. Причината за това се отнася до втория процес, извършен от модула seg_display.

На платка basys3 сегментният дисплей има общи катоди. Докато анодите контролират коя цифра е включена, катодите контролират кои сегменти са включени. Тъй като дисплеят има общи катоди, това означава, че можете да показвате само един набор от сегменти наведнъж. Това поставя проблем за този проект, тъй като искаме едновременно да покажем буква на първата цифра и плоския символ, ако е необходимо. Спомнете си сега сигнала на часовника от 7 секунди? За да заобиколим този проблем, ние сменяме анодите и катодите напред и назад по сигнала на часовника 7seg. Тъй като часовникът е 240 Hz и използваме две цифри, всяка цифра ще се колебае при 60 Hz. За човешкото око ще изглежда, че цифрите изобщо не се колебаят.

Също така имайте предвид, че дисплеят на дъската basys3 използва отрицателна логика. Това означава, че ако анод или катод е зададен на „0“, тази цифра или сегмент ще бъде включен и обратно.

Входове

- Pitch (двоично число за нота, използвано в състояние на възпроизвеждане)

- Freq (честотни превключватели, използвани в състояние на избор)

- P_state (сегашно състояние от PPS FSM)

- Clk_240Hz (часовник сигнал от Clk_div_7seg, двойно 120, защото използваме само нарастващия ръб)

Изходи

- Катод (шина, която контролира сегменти на дисплея, краен изход)

- Анод (шина, която контролира цифрите на дисплея, краен изход)

Компоненти

- Фиксатор

- MUX

- D регистър

Стъпка 15: Окончателен избор

Окончателният избор е последният модул, използван в този проект. Друг прост модул, този модул контролира крайния изход, който ще бъде насочен към DAC. Когато е в състояние "избор" или "пауза", модулът ще изведе статично "0000", така че да не се възпроизвежда музика от високоговорителите. В състояние "възпроизвеждане" модулът ще изведе осцилиращите 4-бита, както е определено от square_wave.

Входове

- P_state (настоящо състояние от PPS FSM)

- DAC_input (осцилиращите 4-бита от square_wave)

Изходи

DAC (равен на DAC_input в състояние на възпроизвеждане, краен изход)

Компоненти

MUX

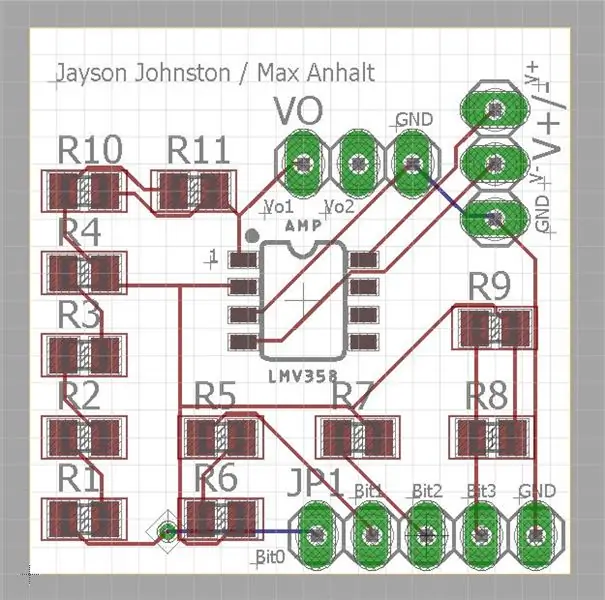

Стъпка 16: Външни устройства: DAC

Цифро -аналоговият преобразувател (DAC) приема дискретен сигнал и го преобразува в непрекъснат сигнал. Нашият DAC има четири бита и е направен от сумиращ усилвател. Използвайки съотношение на резистори в веригата за захранване и обратна връзка, успяхме да създадем система, която извежда на 16 различни нива, създавайки чрез "сумиране" на всеки клон. Bit0, най -горният клон, носи най -малкото тегло и допринася за най -малкия потенциал, когато е висок поради това разклоненията по -голямо съпротивление. Теглото се увеличава, когато слизате по клоните. Ако трябва да броите в двоично нагоре и след това обратно обратно, използвайки битовите входове, изходното напрежение би изглеждало като стъпаловидна синусова вълна. Входът към DAC е свързан към един от PMOD на платката за прехвърляне на 4-битовия сигнал.

ЦАП първоначално е бил сглобен за клас по електротехника и е проектиран и запоен от нас, а не закупен от магазин. По -горе е изображение на дизайнерския файл за създаване на печатна платка.

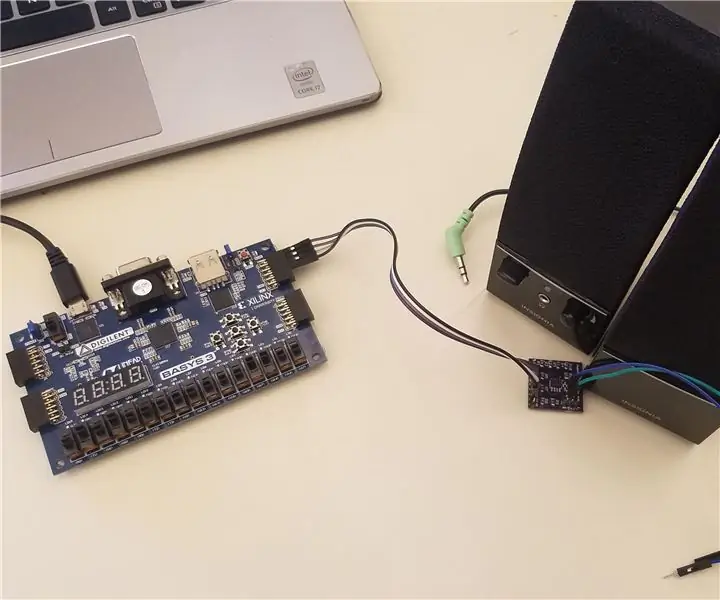

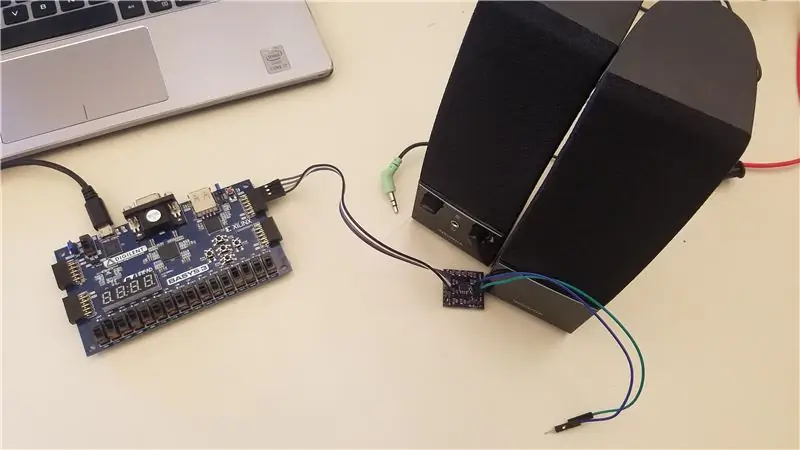

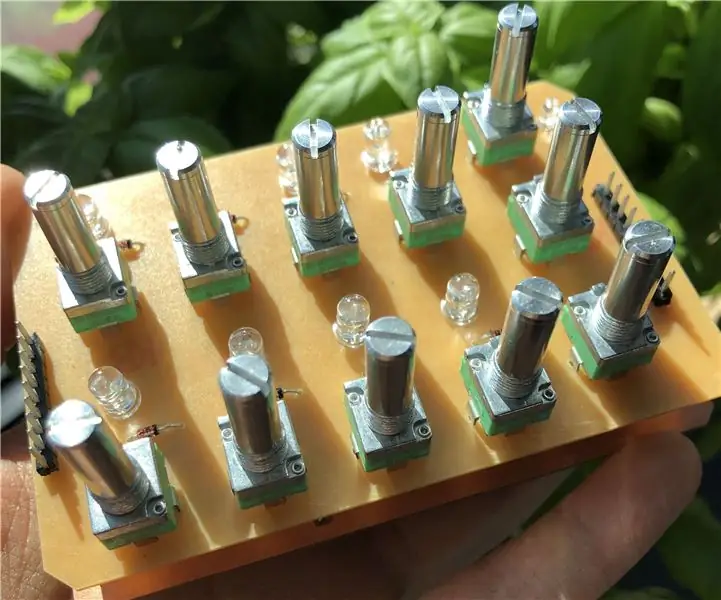

Стъпка 17: Външни устройства: Високоговорител

За този проект няма да искате да купите супер хубав чифт високоговорители. Както можете да кажете, звукът е доста основен. Отидохме и купихме комплект компютърни високоговорители за 8 долара от Best Buy. Всичко с жак за слушалки работи добре. Монотонният също работи добре. Можете дори да използвате слушалки, но може да ги взривите!

За да свържете изхода на DAC към високоговорителите, използвахме джъмперни кабели и след това държахме изходния кабел към върха на жака за слушалки и кабела за заземяване към основата. Опитахме да използваме електрическа лента, за да държим кабелите на място, но това предизвика много смущения. Опитът с различен стил на лента може да реши този проблем.

За нашите високоговорители ги насочихме към най -високата настройка и получихме прилично силен шум.

И това е последната стъпка за създаване на цифров секвенсор от FPGA платка! Отидете на следващите два раздела, за да изтеглите целия наш VHDL код и да видите секвенсора в действие.

Стъпка 18: Видео демонстрация

Това видео показва окончателната версия на работния проект, включително процеса на разпределяне на превключвателите на 4 различни височини и ораторите, които свирят съответните ноти.

Стъпка 19: VHDL код

Ето кода за целия проект, включително ограниченията и sim файловете, използвани при изграждането на секвенсора. Имайте предвид, че неизползваните дизайнерски файлове казват така в архитектурата.

Препоръчано:

Синтез на паралелен секвенсор: 17 стъпки (със снимки)

Parallel Sequencer Synth: Това е ръководство за създаване на прост секвенсор. Секвенсорът е устройство, което циклично произвежда поредица от стъпки, които след това управляват осцилатор. Всяка стъпка може да бъде присвоена на различен тон и по този начин да създаде интересни последователности или аудио ефекти

Прост секвенсор: 16 стъпки (със снимки)

Прост секвенсор: Един от ключовете за правене на добра музика е безмисленото повторение. Именно в това се справя простият секвенсор. Той прави едно и също нещо отново и отново в последователност от осем бележки. Можете да регулирате честотата на бележката, продължителността на бележката и

Atari Punk Console с бебе 8 секвенсор за стъпки: 7 стъпки (със снимки)

Atari Punk Console с Baby 8 Step Sequencer: Тази междинна конструкция е всичко в едно Atari Punk Console и Baby 8 Step Sequencer, които можете да фрезерате на настолна PCB фреза на Bantam Tools. Състои се от две платки: едната е платка с потребителски интерфейс (UI), а другата е помощна програма bo

(почти) Универсален MIDI SysEx CC програмист (и секвенсор ): 7 стъпки (със снимки)

(почти) Универсален MIDI SysEx CC програмист (и секвенсор …): В средата на осемдесетте години производителите на синтезатори започнаха „по -малко е по -добре“процес, който доведе до синтезатори barebones. Това позволи намаляване на разходите от страна на производителя, но направи процеса на закърпване достъпен, ако не и невъзможен за крайната употреба

Програмируем RGB LED секвенсор (използвайки Arduino и Adafruit Trellis): 7 стъпки (със снимки)

Програмируем RGB LED секвенсор (използвайки Arduino и Adafruit Trellis): Синовете ми искаха цветни LED ленти да осветяват бюрата си и не исках да използвам консервиран RGB лентов контролер, защото знаех, че ще им омръзне фиксираните модели тези контролери имат. Мислех също, че това ще бъде чудесна възможност да създам