Съдържание:

- Стъпка 1: Създаване на проект във Vivado за Ърни

- Стъпка 2: Създаване на PWM на Ernie във Vivado

- Стъпка 3: Създаване на TDOA на Ernie във Vivado

- Стъпка 4: Опаковане и експортиране на Ърни

- Стъпка 5: Изграждане на Ърни

- Стъпка 6: Първият BSP на Ърни

- Стъпка 7: FreeRTOS'ing Ernie

- Стъпка 8: Импортиране на C код на Ernie

- Стъпка 9: Отстраняване на грешки Ernie

- Стъпка 10: Направете Ernie автономен

- Стъпка 11: Направете Ърни сладък

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 07:50.

- Последно модифициран 2025-01-23 12:57.

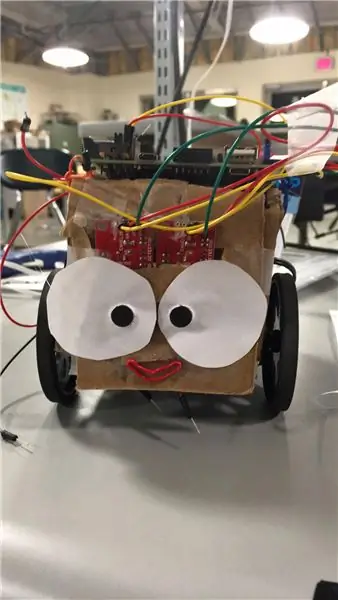

Това е урок за това как да изградите Ernie, вашия автономен звук след робот, използвайки Zybo Board. Той ще обхваща как да: създадете проект във Vivado, да създадете PWM-подобни драйвери на серво мотори във FPGA, интерфейс с два звукови сензора, да създадете разлика във времето на IP за пристигане, да използвате freeRTOS и да стартирате zybo от батерия. Това беше последният ни проект за клас Операционни системи в реално време (CPE 439) в Cal Poly SLO.

Списък на оборудването:

- 1 - Съвет за развитие на ZYBO Zynq 7000

- 2 - Серво за непрекъснато въртене на паралакс

- 2 - Звуков сензор (SparkFun звуков детектор)

- 1 - 5v литиево -йонна USB батерия (за платка)

- 4 - батерии тип АА (за сервоустройства)

- 1 - AA батерия (с/ 4 гнезда за батерии)

- 1 - Micro USB кабел

- 1 - Платка

- много - мъжки към мъжки проводници

- 1 - Серво шаси

Софтуерни изисквания:

- Xilinx Vivado Design Suite 2016.2

- Digilent Adept 2.16.1

Стъпка 1: Създаване на проект във Vivado за Ърни

- Ще се появи съветник

- Щракнете върху Напред

-

Следващото име на проекта

- Никога не използвайте име на проект или пътека на директорията, в която има интервали !!!!!

- Това ще бъде RTL проект.

- Не искаме да посочваме източници

-

Щраквайки върху Напред, стигаме до страницата Част. Използваме ZYNQ XC7Z010-1CLG400C.

- Vivado няма Zybo, посочен като една от предварително зададените му дъски. Изберете: „части“, след което потърсете xc7z010clg400-1.

- Ако погрешно изберете грешната част, лесно можете да превключите чипове: Инструменти -> Настройки на проекта -> Общи и щракнете върху точките вдясно от „Устройство за проект“

-

Щракнете върху Създаване на дизайн на блок.

Дайте му името design_1 засега

- Ще видите зелена лента с надпис Добавяне на IP, щракнете върху нея.

-

Търсете Zynq.

- Щракнете двукратно върху ZYNQ7 Processing System,

- Този блок ще се появи в нашия блок дизайн.

- Ще видите зелена лента, на която пише Run Block Automation, щракнете върху нея.

- Изтеглете zybo_zynq_def.xml по -долу.

-

В Vivado щракнете върху „Импортиране на XPS настройки“и изберете „zybo_zynq_def.xml“

Това предварително попълва конфигурацията на блока Vivado с всички вградени периферни устройства и щифтове на Zybo платка

-

Щракнете двукратно върху блока ZYNQ.

-

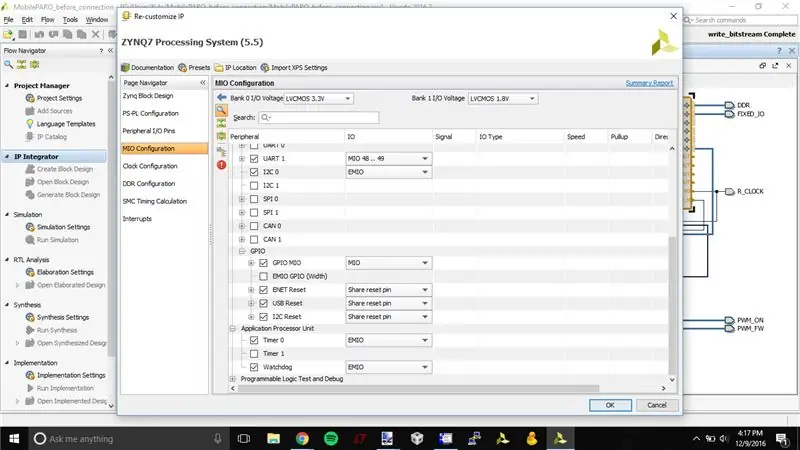

MIO конфигурация

- Активиране на таймер 0 (под модул за процесор на приложения - img 1)

- Активиране на Watchdog (под модул за процесор на приложения- img 1)

- Активиране на GPIO-> GPIO MIO (под модул за процесор на приложения - img 2)

- Активиране на GPIO-> ENET Reset (под I/O периферия- img 2)

-

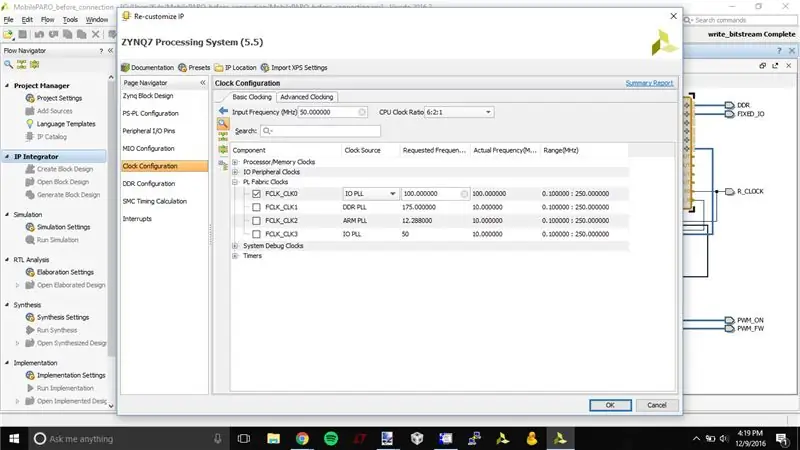

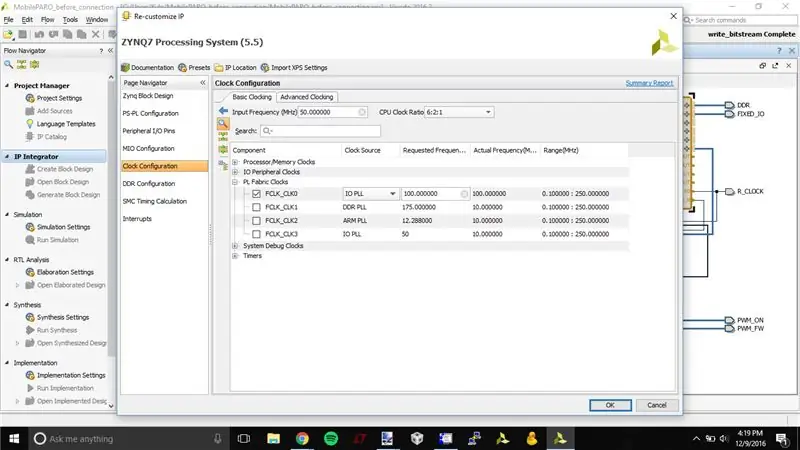

Конфигурация на часовника

Деактивирайте FCLK0 (под PL Fabric Clocks - img 3)

-

- Щракнете върху OK.

-

„Стартирайте автоматизацията на блокове“сега.

Ще има някои въпроси относно сигналите, кажете OK

-

Щракнете върху „Генериране на HDL обвивка“.

Ще искаме да копираме генерираната обвивка, за да позволим потребителски редакции

- Щракнете върху OK.

Стъпка 2: Създаване на PWM на Ernie във Vivado

Тази стъпка ще генерира PWM IP с входове, изпратени чрез AXI библиотеката.

-

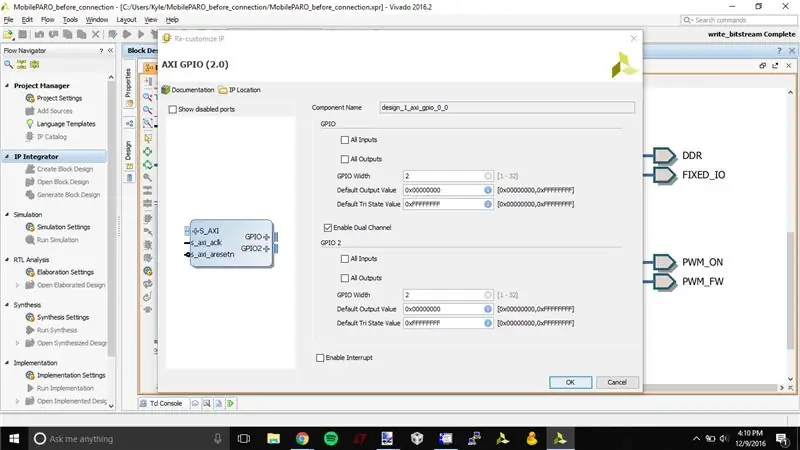

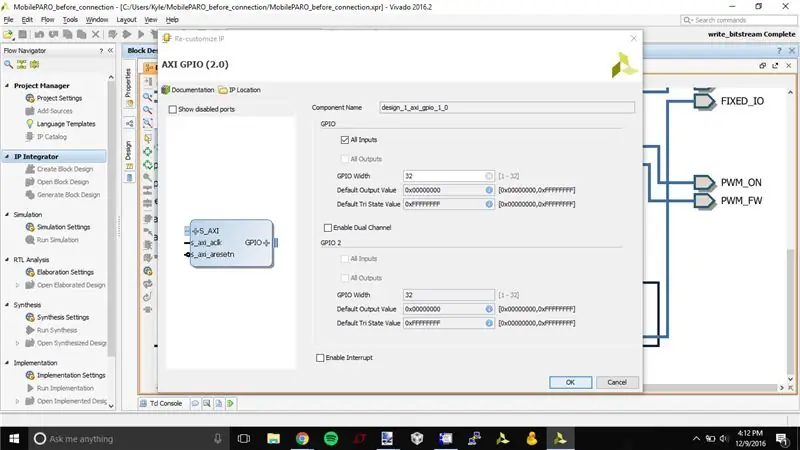

Създайте AXI GPIO блок, като щракнете с десния бутон върху фона и щракнете върху „добавяне на IP“

въведете „AXI_GPIO“в лентата за търсене и изберете този пакет

-

Повторно персонализирайте IP, като щракнете двукратно върху новия блок axi_gpio_0

- при GPIO, задайте ширина на GPIO на 2. Тези битове ще бъдат PWM_ON сигнал за задвижване на всеки екземпляр на PWM модул.

- кликнете върху „активиране на двоен канал“

- при GPIO 2, задайте ширина на GPIO на 2. Тези битове ще бъдат PWM_FW сигнал, за да зададете посоката на всеки екземпляр на PWM модул.

-

Щракнете с десния бутон върху изходния порт axi_gpio_0, обозначен с GPIO, и изберете „Направи външно“

- Щракнете върху новия изход с етикет GPIO и отидете в раздела "свойства" в лявата лента с инструменти и променете името на PWM_ON

- Щракнете върху новия изход с етикет GPIO2 и отидете в раздела "свойства" в лявата лента с инструменти и променете името на PWM_FW

-

Изберете Run Connection Automation в зеления банер над блоковата диаграма.

Ако свържете ръчно портовете, AXI адресите може да не бъдат конфигурирани, което да доведе до проблеми с комуникацията по -късно

-

В панела Flow Navigator изберете мениджър на проекти -> Добавяне на източници, за да създадете нов персонализиран IP блок

- изберете „добавяне или създаване на източници на дизайн“и натиснете следващия

- щракнете върху „създаване на файл“, променете типа на файла на „SystemVerilog“и въведете „pwm“в полето за име на файл, след което щракнете върху OK

- щракнете върху Готово

-

игнорирайте прозореца Дефиниране на модул, като натиснете OK (ще ги презапишем по -късно)

ако ви попита дали сте сигурни, щракнете върху Да

-

В раздела източници щракнете двукратно върху pwm.sv (намира се в „Design Sources/design_1_wrapper“)

Копирайте/поставете целия код на SystemVerilog от прикачения по -долу pwm.txt файл

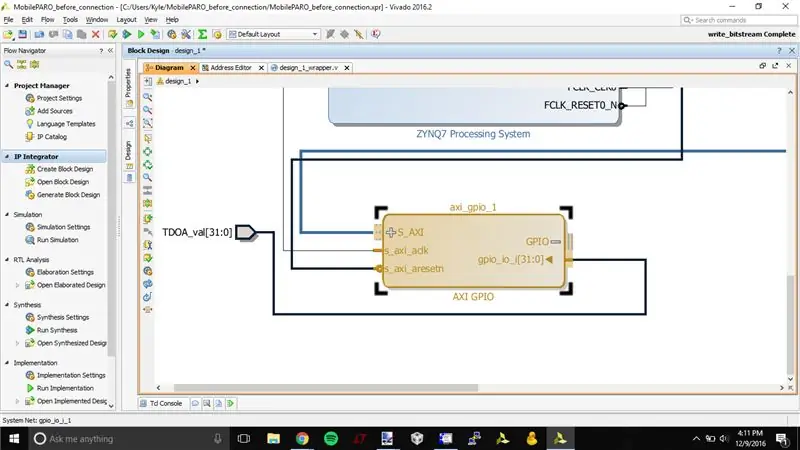

Стъпка 3: Създаване на TDOA на Ernie във Vivado

Тази стъпка ще генерира TDOA IP, чийто изход може да бъде прочетен чрез AXI библиотеката

-

Създайте AXI GPIO блок, като щракнете с десния бутон върху фона и щракнете върху „добавяне на IP“

въведете „AXI_GPIO“в лентата за търсене и изберете този пакет

-

Повторно персонализирайте IP, като щракнете двукратно върху новия блок axi_gpio_1

- под GPIO, поставете отметка в квадратчето „Всички входове“и задайте ширина на GPIO на 32. Тази шина ще бъде разликата във времето на пристигане между двата сензора.

- вътре в блока axi_gpio_1, щракнете върху + до GPIO порта, за да разкриете gpio_io_i [31: 0].

-

Щракнете с десния бутон върху изходния порт на axi_gpio_1 с надпис gpio_io_i [31: 0] и изберете „Направи външно“

Щракнете върху новия вход, обозначен с gpio_io_i [31: 0], и отворете раздела "свойства" в лявата лента с инструменти и променете името на TDOA_val

-

Изберете Run Connection Automation в зеления банер над блоковата диаграма.

Ако свържете ръчно портовете, AXI адресите може да не бъдат конфигурирани, което да доведе до проблеми с комуникацията по -късно

-

В панела Flow Navigator изберете мениджър на проекти -> Добавяне на източници, за да създадете нов персонализиран IP блок

- изберете „добавяне или създаване на източници на дизайн“и натиснете следващия

- щракнете върху „създаване на файл“, променете типа на файла на „SystemVerilog“и въведете „tdoa“в полето за име на файл, след което щракнете върху OK

- щракнете върху Готово

-

игнорирайте прозореца Дефиниране на модул, като натиснете OK (ще ги презапишем по -късно)

ако ви попита дали сте сигурни, щракнете върху Да

-

В раздела източници щракнете двукратно върху tdoa.sv (намира се в „Design Sources/design_1_wrapper“)

Копирайте/поставете целия код на SystemVerilog от прикачения по -долу файл tdoa.txt

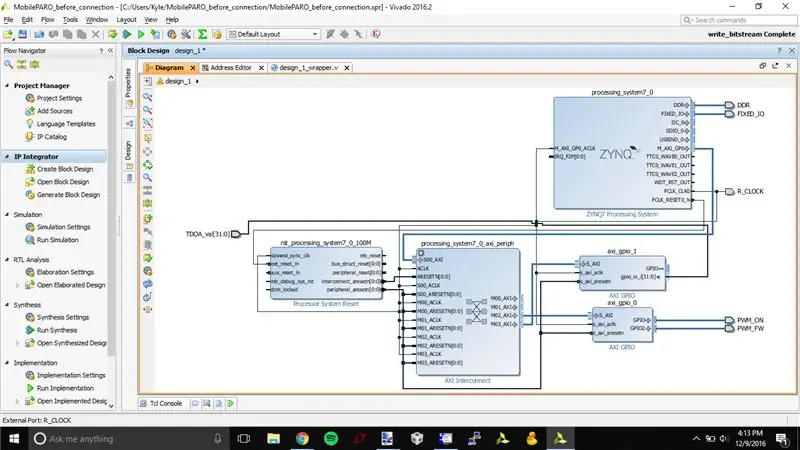

Стъпка 4: Опаковане и експортиране на Ърни

- Проверете дали блоковата диаграма изглежда като прикачения екран

-

В раздела източници щракнете с десния бутон върху design_1.bd и изберете „Създаване на HDL обвивка …“

- Изберете „Копиране на генерирания изход, за да разрешите потребителски редакции“, след това натиснете „OK“

- Копирайте кода от приложен по -долу design_1_wrapper.txt и го поставете на мястото на генерирания код design_1_wrapper.v

- запазете design_1_wrapper.v

-

В раздела източници щракнете двукратно върху файла ZYBO_Master.xdc под Ограничения/constrs1

- Копирайте кода от прикачения по -долу ZYBO_Master.txt и го поставете на мястото на съществуващия код ZYBO_Master.xdc

-

Обърнете внимание на следните входни/изходни щифтове:

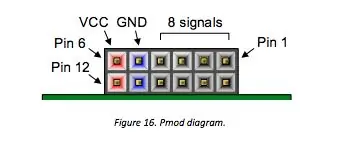

- L15: ШИМ сигнал за левия двигател (Pmod JA2 на Zybo)

- L14: ШИМ сигнал за десния двигател (Pmod JA8 на Zybo)

- V12: вход на порта от звуков сензор 1 (Pmod JE1 на Zybo)

- K16: вход на порта от звуков сензор 2 (Pmod JE2 на Zybo)

-

В екрана за навигация на потока щракнете върху „Генериране на поток от битове“под Програма и отстраняване на грешки

ако мислите, че е направено веднага, вероятно не е така. сериозно, направете си чай

-

Щракнете върху Файл-> Експорт-> Генериране на хардуер

Поставете отметка в „Включване на битстрийм“и натиснете OK

- Щракнете върху Файл-> Стартиране на SDK

Стъпка 5: Изграждане на Ърни

- Монтирайте сервомоторите към серво шасито.

-

Следвайки листа с данни за сервомоторите, направете следното:

- свържете заземяването на сервомоторите към заземяващи щифтове на JA Pmod на Zybo (вижте приложеното изображение на разклонение)

- свържете захранващия щифт на сервомоторите към батерията AA

Открихме, че когато сервомоторите са свързани към Vdd на Zybo, платката черпи твърде много ток, което води до непрекъснато нулиране на платката

- свържете щифтовете на входния сигнал към подходящите изходни щифтове на Zybo (вляво: JA2, вдясно: JA8)

- монтирайте звуковите сензори към предната част на шасито, обърнати напред, като ги държите възможно най -близо един до друг

-

използвайте ръководството за свързване на сензора за звук, за да интегрирате звуковите сензори

- свържете заземяването и Vdd щифтовете на всеки звуков сензор към земята и Vdd щифтовете на JE Pmod на Zybo (вижте приложеното изображение на разклонение)

- свържете левия щифт на левия сензор за звук към JE1

- свържете десния щифт на десния сензор за звук към JE2

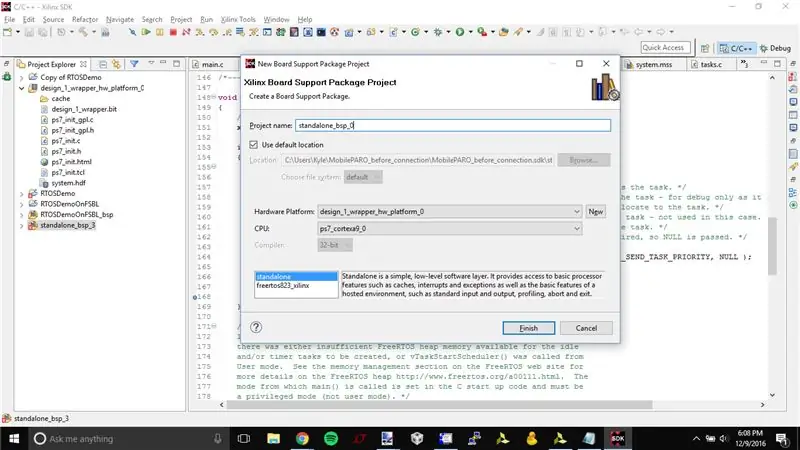

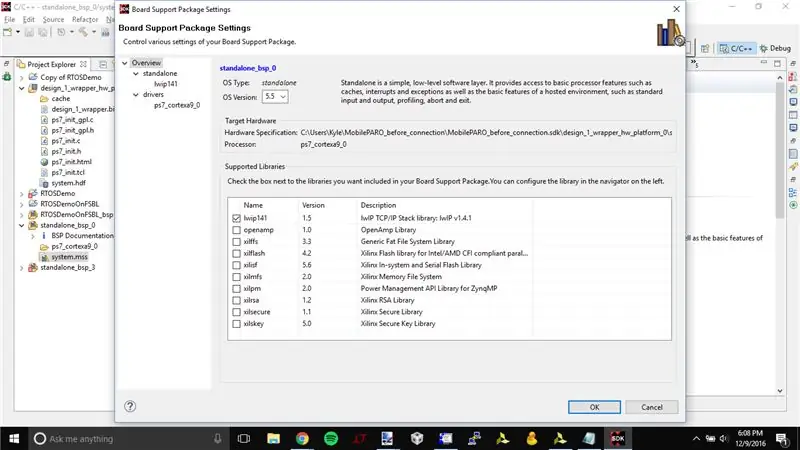

Стъпка 6: Първият BSP на Ърни

-

Създайте BSP, за да завършите платформата, която току -що създадохме.

Можете да получите това чрез File -> New -> Board Support Package

-

Ще се появи съветник, който ще ви помогне да създадете BSP.

- Искаме да обвържем тази BSP с нашата платформа, която току -що създадохме, така че

- Хардуерната платформа трябва да съвпадне с тази, която току -що създадохме (вижте img 1)

- Нашият процесор ще бъде _0 процесор.

- Щракнете върху Готово

- Не забравяйте да проверите lwip141 за включване с вашия bsp в изскачащия прозорец (вижте img 2)

Стъпка 7: FreeRTOS'ing Ernie

-

Изтеглете последната версия на FreeRTOS от Sourceforge.

Ако изтеглянето е изпълним, стартирайте го, за да извлечете FreeRTOS файловете в директорията на вашия проект

- Дръжте този SDK отворен и щракнете върху Файл -> Импортиране.

- Искаме да щракнем върху Общи-> От съществуващо работно пространство и след това ще искаме да отидем до мястото, където сме изтеглили FreeRTOS.

-

Нашето демо ще се намира в FreeRTOS/Demo/CORTEX_A9_Zynq_ZC702. При избора на тази папка трябва да видим изскачащи три проекта (нашият код (OS), това е BSP и платформата HW).

САМО Импортирайте RTOSDemo в текущото си работно пространство

-

На всички проекти „сини“папки променете референтния BSP

- Щракнете с десния бутон и изберете „Промяна на референтния BSP“.

- Изберете BSP, който току -що създадохте за вашия Zybo

- Редактирането на кодове в папки SDK Blue на Xilinx са действителните кодови проекти.

Стъпка 8: Импортиране на C код на Ernie

- В директорията RTOSDemo/src презапишете съществуващия main.c с прикачения тук файл main.c.

- Копирайте файла main_sound.c в директорията RTOSDemo/src.

Стъпка 9: Отстраняване на грешки Ernie

- Изберете Run -> Debug Configurations

- В левия прозорец създайте ново изпълнение на System Debugger

-

В раздела Настройка на целта,

изберете „Нулиране на цялата система“, така че и това, и ps7_init да бъдат избрани

-

Сега изберете раздела Приложение.

- Изберете „изтегляне на приложение“

- Задайте ядрото cortexa9_0 на „стоп при влизане в програмата“

- Щракнете върху Прилагане и отстраняване на грешки.

- Проверете дали няма грешки в процеса на отстраняване на грешки

- Като следите отблизо робота, натиснете бутона Възобновяване, докато програмата работи, без да удряте точки на прекъсване

- Сега роботът трябва да се обърне и да се придвижи към силни шумове. Да!

Стъпка 10: Направете Ernie автономен

- След като вашият проект е готов за стартиране (можете да стартирате без проблеми чрез дебъгъра), вие сте готови да го заредите във флаш паметта на вашата дъска.

-

Създайте така наречения проект за първоначално зареждане (FSBL) и съдържа всички инструкции, от които вашата платка ще се нуждае, за да зареди файловете на вашия проект (битовия поток и операционната система) при стартиране.

- Изберете: File-> New-> Application Project и следващият прозорец трябва да се появи.

- Назовете го както искате (т.е. „FSBL“)

- Уверете се, че хардуерната платформа е тази, с която работите

- Натиснете следващия (Не натискайте Край)

- Изберете шаблона Zynq FSBL

- Щракнете върху Край.

- След като процесът на създаване приключи, ще разберете дали всичко е работило, ако видите следните две нови папки в прозореца на Project Explorer.

-

Създаване на зареждащо изображение Сега ще трябва да създадете зареждащо изображение.

- Щракнете с десния бутон върху папката на вашия проект (в този случай моята се нарича „RTOSDemo“)

- Щракнете върху „Създаване на зареждащо изображение“от падащото меню

-

Ако всичко е свързано правилно, проектът ще знае от какви файлове се нуждае и следният прозорец ще изглежда, както виждате по -долу (ключовото е, че имате 3 дяла в секцията Boot image, буутлоудъра, вашия битов файл и вашите.elf файл на вашите проекти).).

Ако това не е така, вероятно нещо не е наред с свързването на вашия проект. Уверете се, че папките на проекта са свързани със съответните им BSP

- Щракнете върху бутона „Създаване на изображение“

-

Последната стъпка, която трябва да извършите в софтуера, е сега да прехвърлите предварително създаденото си изображение в паметта на дъската

- Изберете от основната лента с инструменти на SDK, изберете Xilinx Tools-> Program Flash Memory

- Уверете се, че е избрана правилната хардуерна платформа и че пътят на файла с изображение правилно сочи файла. BIN, създаден в предишната стъпка.

- Изберете „qspi single“от типа Flash

- Поставете отметка в „Verify after flash“, за да осигурите целостта, но това не е необходимо

- Конфигурирайте вашата платка Накрая трябва да се уверите, че джъмпера за програмиране на платки (JP5) е правилно настроен да избира за зареждане от qspi (който съдържа това, което току -що мигате), когато се стартира BootROM.

- Сега просто включете захранването на устройството и се уверете, че светодиодът „Logic Configuration Done“(LED 10) свети в зелено.

Стъпка 11: Направете Ърни сладък

- Козина

- Много кожа

- Големи очи!

- … цилиндър

Препоръчано:

Как да си направим безжичен телефон с консерва! (Уоки токи Arduino): 7 стъпки (със снимки)

Как да си направим безжичен телефон с консерва! (Ардуино уоки токи): Точно онзи ден бях в средата на много важно телефонно обаждане, когато банановият ми телефон спря да работи! Бях толкова разочарован. Това е последният път, когато пропускам обаждане заради този глупав телефон! (Като се върна назад, може би малко се ядосах

Как да си направим линеен задвижващ механизъм: 3 стъпки

Как да си направим линеен задвижващ механизъм: Линейните задвижващи механизми са машини, които преобразуват въртенето или всяко движение в движение с натиск или издърпване

КАК ДА НАПРАВИМ ARDUINO NANO/MINI - Как да запишете Bootloader: 5 стъпки

КАК ДА НАПРАВИМ ARDUINO NANO/MINI | Как да запиша Bootloader: В тази инструкция ще ви покажа как да направите Arduino MINI от нулата. Процедурата, написана в тази инструкция, може да се използва за направата на всякакви дъски arduino за вашите изисквания по проект. Моля, гледайте видеото за по -добро разбиране на

Музикална реактивна светлина -- Как да направим супер проста музикална реактивна светлина, за да направим работния плот привлекателен .: 5 стъпки (със снимки)

Музикална реактивна светлина || Как да направим супер проста музикална реактивна светлина за създаване на страхотен работен плот. Хей какво става, момчета, днес ще изградим много интересен проект. Днес ще изградим реактивна музикална светлина. Светодиодът ще промени яркостта си според басът, който всъщност е нискочестотен аудио сигнал. Изграждането му е много просто. Ние ще

Как да си направим календар на баба и дядо & Записник (дори ако не знаете как да записвате): 8 стъпки (със снимки)

Как да си направим календар на баба и дядо & Записник (дори и да не знаете как да записвате): Това е много икономичен (и много ценен!) Празничен подарък за баби и дядовци. Направих 5 календара тази година за по -малко от $ 7 всеки. Материали: 12 страхотни снимки на вашето дете, деца, племенници, племенници, кучета, котки или други роднини12 различни парчета