Съдържание:

- Стъпка 1: Импортирайте дадените VHDL файлове

- Стъпка 2: Разбивка на горния модул на VHDL

- Стъпка 3: Разбиване на VHDL Kill Switch модул

- Стъпка 4: Разбивка на VHDL флип флоп модул

- Стъпка 5: Разбивка на VHDL Piezo Buzzer модул

- Стъпка 6: Разбиване на файла с ограничения на VHDL

- Стъпка 7: Изграждане на основите 3

- Стъпка 8: Внедряване на VHDL файлове в бази 3

- Стъпка 9: Използване на дъската Basys 3

- Стъпка 10: Покажете се

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 07:53.

- Последно модифициран 2025-01-23 14:36.

Уморихте ли се да проверявате дали всички светлини в къщата ви са изключени, преди да заспите? Искате ли да можете да изключите всяка светлина наведнъж без никакъв шум? За да спестим енергия и време, решихме да създадем система, която теоретично може да затвори цяла къща наведнъж.

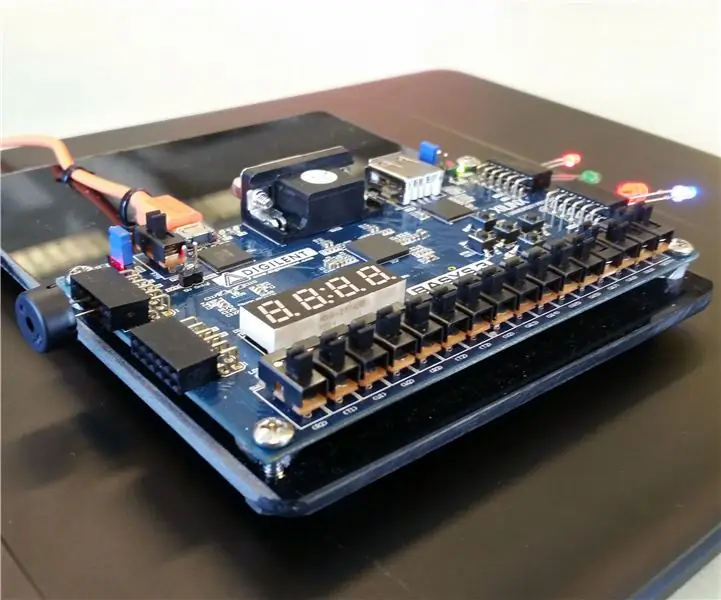

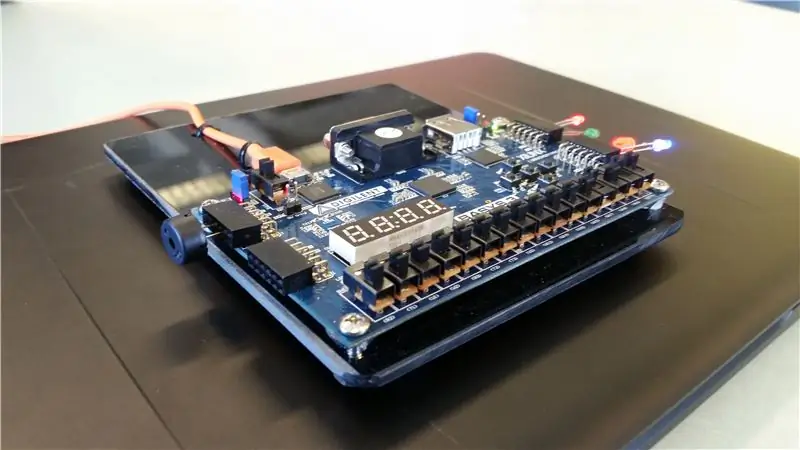

Ние моделирахме доказателство за тази концепция, използвайки няколко светодиода и основна платка 3 и създадохме дизайн, който да деактивира всички светодиоди с натискане на бутон. Този модел може да се приложи и към действителна система за домашно осветление, въпреки че ще изисква по -сложно окабеляване и модификации на дадените VHDL файлове.

Стъпка 1: Импортирайте дадените VHDL файлове

За да работи правилно нашият модел, ще трябва да изтеглите софтуера, който дава инструкциите на дъската Basys 3.

Първо ще трябва да изтеглите инструмент за синтез за внедряване на vhdl файлове на хардуер. Ако искате да сте сигурни, че целият код ще възпроизведе изцяло нашия дизайн, без да се налага никакви промени, препоръчваме да използвате Vivado 2016.2. След като инсталирате Vivado, можете да създадете проект и да изтеглите нашите изходни файлове. Добавете ги като източници към вашия проект, не забравяйте да добавите и файла с ограничения!

След това ще обясним какво прави всеки от изходните файлове. Прескочете стъпки 2 до 6, ако просто искате да стигнете до физическата конструкция на устройството.

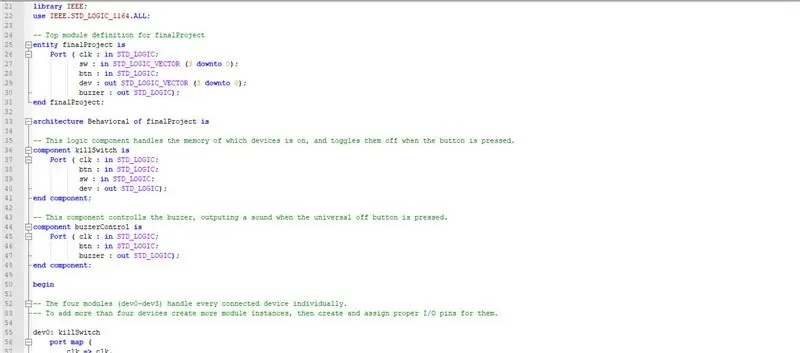

Стъпка 2: Разбивка на горния модул на VHDL

Най -горният модул на проекта е това, което свързва всички отделни модули на компонентите с използвания хардуер. Както можете да видите, модулите killSwitch и buzzerControl са дефинирани като компоненти отгоре.

Долната част определя как тези модули са свързани заедно. Свързахме четири светодиода към платката и ги свързахме с модулите killSwitch от dev0 до dev3. Имаме дефинирани четири killSwitch модула, защото се нуждаем от един за управление на състоянието на всеки свързан светодиод. Всеки от тези модули използва часовника и сигнала от бутоните, които създадохме в горната дефиниция на модула, както и съответните им входни превключватели и сигнали на изходното устройство.

Модулът за управление на зумера в долната част активира зумера, когато се натисне универсалният бутон за изключване. Както можете да видите, модулът за управление на зумера се предава на часовника и сигнала на бутона като входове. Предава се и изходният извод на физически зумер, за да се управлява съответно.

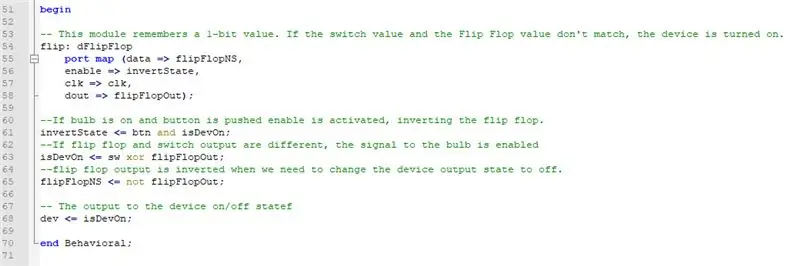

Стъпка 3: Разбиване на VHDL Kill Switch модул

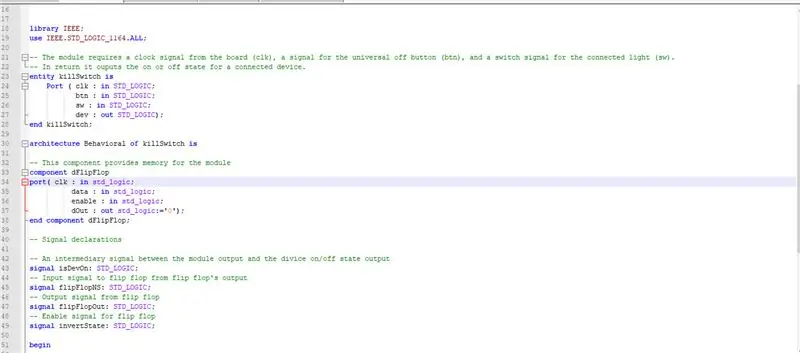

Kill Switch е универсалният бутон за изключване и модулът се занимава предимно с свързването му към други елементи на веригата, така че при натискане всички светлини да се изключат.

Докато горният модул обработва свързването на физически хардуер към софтуера, модулът killSwitch обработва основната логика на всяко устройство. Модулът приема входове за часовника, универсалния бутон за изключване и превключвателя на устройството. В замяна той контролира състоянието на щифта на устройството, към който е свързан.

В раздела за архитектура на кода виждаме, че той има зависимост от модула dFlipFlop за съхраняване на памет. Можете също така да видите, че сме декларирали четири сигнала, които ще бъдат използвани за свързване на джапанките, както и за изпълнение на нашите логически изявления. В рамките на поведенческата секция на кода създадохме екземпляр на модула dFlipFlop и зададохме нашите I/O сигнали към портовете.

От тук основната част от нашата логика се крие в стойностите на сигнала за invertState и isDevOn. Нашата логическа основа за устройството е следната: "Всеки път, когато превключвателят е хвърлен, светлината ще обърне състоянието си за включване/изключване. Всеки път, когато бутонът е натиснат и светодиодът в момента е включен, светодиодът ще обърне състоянието си на изключено. " От тези две твърдения можем да екстраполираме, че състоянието на светодиода трябва да бъде XOR на превключвателя и нашия елемент на паметта. По този начин промяната в някое от двете инвертира светодиода. Това може да се види реализирано в сигнала isDevOn. Светодиодът при условие за елемента памет се управлява от нашия сигнал invertState. Ако светодиодът свети и бутонът е натиснат, нашият елемент от паметта ще се актуализира и ще обърне състоянието си. Това след това обръща и състоянието на светодиода.

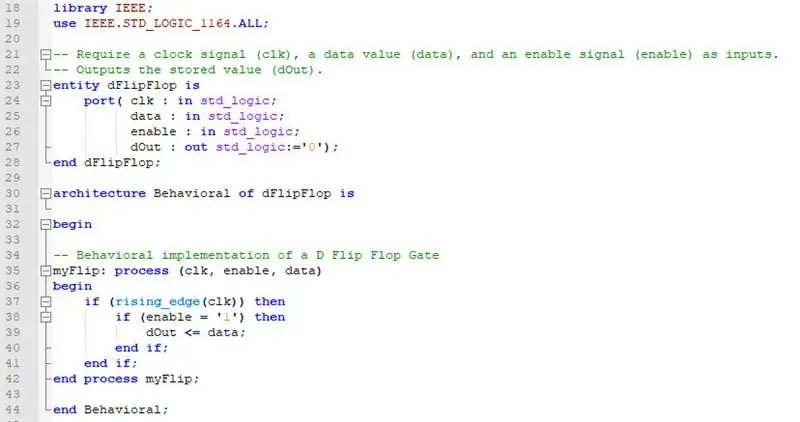

Стъпка 4: Разбивка на VHDL флип флоп модул

Един проблем с нашия дизайн беше фактът, че след използване на превключвателя за изключване, светлините, които преди това бяха включени, може да се наложи да се обърнат два пъти, за да се върнат в положение "включено". Това би било доста неудобство за хората с течение на времето. Успяхме да заобиколим това неудобство, като включихме „Flip Flop“, елемент на верига, способен да съхранява информация, в нашия дизайн. Сега системата помни дали преди това е бил включен светлинен превключвател, така че ако се обърне отново, той ще се включи независимо от първоначалното си положение.

Кодът на VHDL използва инструкции if и else, за да създаде джапанката като компонент в нашия дизайн на веригата. Той гарантира, че когато сигналът на часовника преминава от ниско към високо състояние, когато крушката е включена и когато бутонът за изключване е натиснат, изходът на джапанките презаписва своя вход. Когато входът е презаписан, джапанката е обърната.

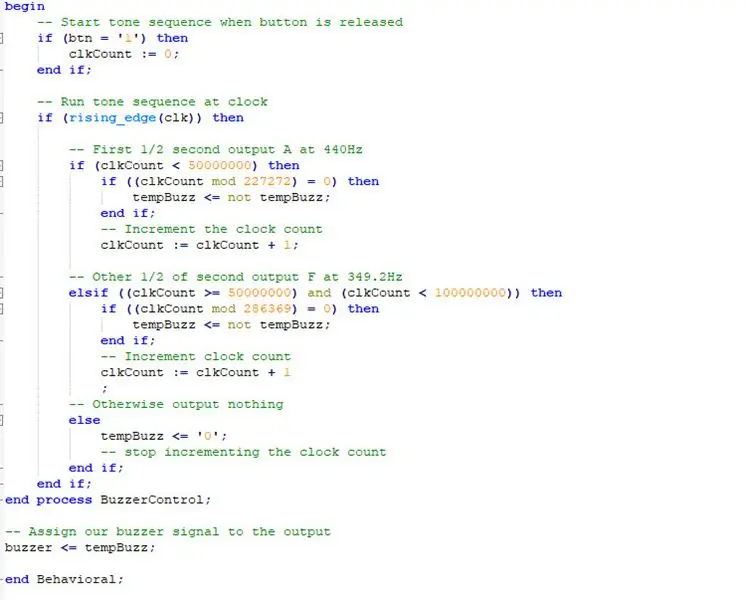

Стъпка 5: Разбивка на VHDL Piezo Buzzer модул

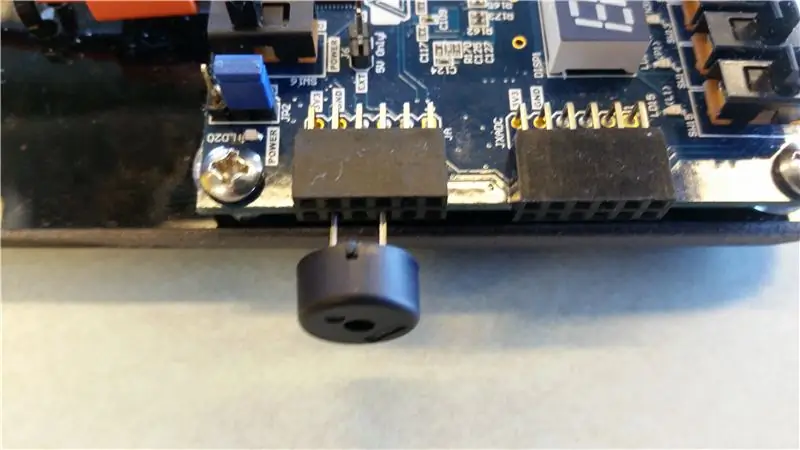

Този файл е малко излишен, що се отнася до хардуерния дизайн, но е от съществено значение, за да може файловете с най -горния модул и ограничения да работят безпроблемно. Ако решите да не използвате пиезо зумера, изтеглете този файл, но не прикрепяйте зумера към платката Basys 3.

Звуковият сигнал на Piezo ще натисне бутона за деактивиране, ще възпроизведе тон с две ноти, който ще предостави на потребителя слухова обратна връзка, че бутонът е натиснат. Ние реализирахме това поведенческо действие във VHDL чрез поредица от оператори if в структурата на процеса. Започнахме със създаване на цяло число, за да следим колко промени на часовника са настъпили. След като процесът започне, програмата прекарва първите половин секунда (0 до 50 милиона часовника), извеждайки бележка А на 440 херца. Това се постига чрез инвертиране на пиезо зумерния сигнал на всеки дори кратен от 227272 часовника с модулна функция. Това число е резултат от разделянето на тактовия сигнал на платката (100 MHz) на желаната честота (400 Hz). През втората половина на секундата (50 до 100 милиона часовника) дъската извежда F бележка на 349,2 херца по същия метод като преди. След една секунда програмата не увеличава допълнително променливата на часовника и спира да извежда нищо от пиезо зумера. Натискането на универсалния бутон за изключване отново нулира този номер на 0, като рестартира цикъла на шума.

Стъпка 6: Разбиване на файла с ограничения на VHDL

Файлът с ограничения казва на Vivado какви устройства на платката Basys 3 използваме. Той също така предоставя на Vivado имената, които дадохме на устройствата в нашия код. Vivado се нуждае от тази информация, за да знае как да свърже нашите логически елементи с физическия хардуер. Файлът с ограничения включва голямо количество коментиран (неизползван) код. Тези редове код посочват устройствата на платката, които не използваме.

Устройствата, които използваме, включват четири входни превключвателя с етикет V17, V16, W16 и W1 на платката. Използваме и универсалния бутон за изключване, обозначен с U18. Изходните щифтове за нашите четири свързани светодиода са JB4, JB10, JC4 и JC10. За нашия пиецо зумер използваме изходен щифт JA9.

Както посочихме в горната разбивка на модула, ако искате да добавите допълнителни светодиоди или други устройства към платката, трябва да увеличите обхвата на сигналите sw и dev, да добавите още модули killSwitch и да ги свържете заедно. След това трябва да свържете тези имена на променливи с хардуера на устройството чрез файла с ограничения. Това може да стане чрез декомментиране (повторно активиране) на редовете от код, свързани с пиновете, които искате да използвате, след което добавете името на свързаната с него променлива в горния модул. Подходящият синтаксис за това може да бъде копиран от устройствата, които използваме. За да разберете имената на щифтовете, които искате да използвате на дъската, вижте справочното ръководство на Baasys 3 тук.

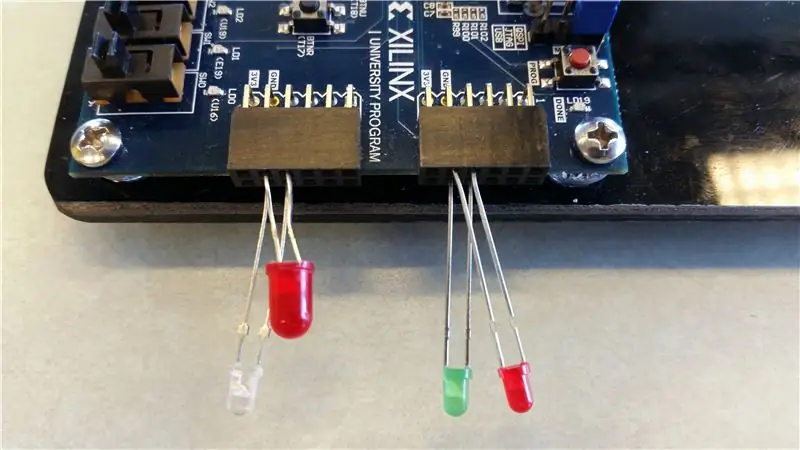

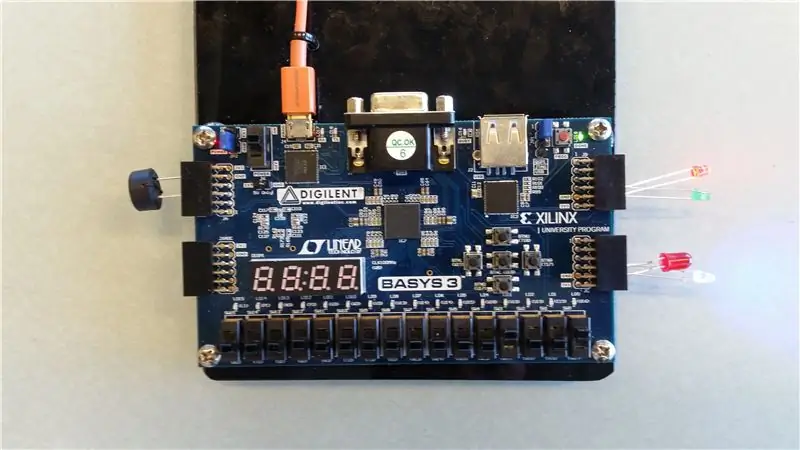

Стъпка 7: Изграждане на основите 3

Ще трябва да включите светодиодите си в правилните I/O портове на Basys 3. Следвайте предоставените снимки, за да определите кои са правилните портове, защото ако включите LED в грешния порт, той няма да светне. Ако сте избрали да прикачите пиезо зумера, ще трябва също да го свържете към правилните I/O портове.

Когато платката е готова, включете я в компютъра си чрез USB кабел.

Стъпка 8: Внедряване на VHDL файлове в бази 3

Сега, когато дъската ви е готова и кодът ви е завършен, най -накрая можете да съберете модела.

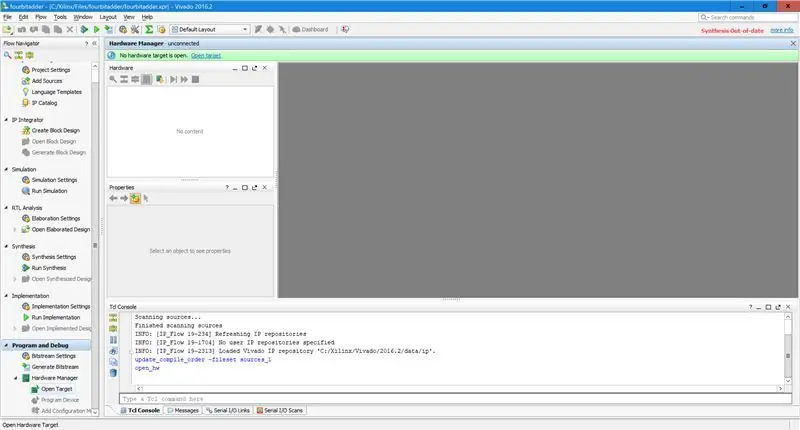

След като настроите вашия проект във Vivado, трябва да кликнете върху бутона „Generate Bitstream“, за да компилирате кода, преди да бъде качен на дъската. Ако получите съобщение за грешка в този момент, трябва да проверите отново дали вашият код съвпада точно с нашия. Когато казвам точно, имам предвид дори точката с запетая или видовете скоби, които се използват. След като вашият поток от битове е записан успешно, отидете на хардуерния мениджър във Vivado и кликнете върху бутона „Open Target“, след което щракнете върху „Program Device“веднага след това. Вашата дъска Basys 3 сега трябва да бъде напълно функционална.

Стъпка 9: Използване на дъската Basys 3

Сега, когато Basys 3 Board е работещ и е програмиран да представя нашия модел, трябва да знаете как да го използвате.

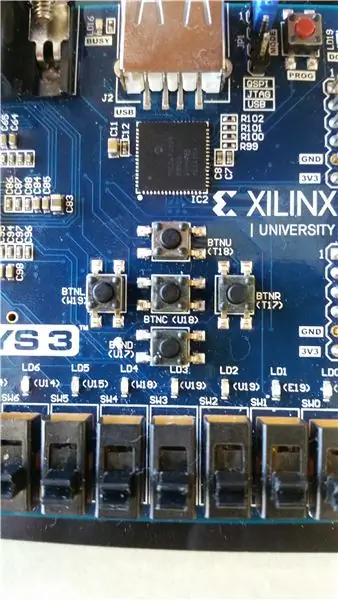

Всеки от четирите превключвателя най -надясно надясно контролира един от светодиодите, като мигането им ще доведе до включване или изключване на светодиода. Ако светодиодът не се активира, проверете дали сте включени в правилния I/O порт и дали вашият светодиод функционира на първо място.

Когато искате да деактивирате всички светодиоди наведнъж, трябва да натиснете централния бутон в набора от пет бутона, показани по -горе.

Стъпка 10: Покажете се

Моделът служи като кокетна малка новост, която можете да демонстрирате пред приятелите и семейството си. Теоретично може да се използва и за внедряване на универсалния превключвател за изключване във вашата домашна електрическа система, ако замените светодиодите с проводници, водещи към вашите светлини. Въпреки че е възможно, все пак трябва да го посъветваме. Имате потенциал да нанесете сериозна вреда на себе си или на дома си, ако се опитате да окабелите без помощта на електротехник.

Препоръчано:

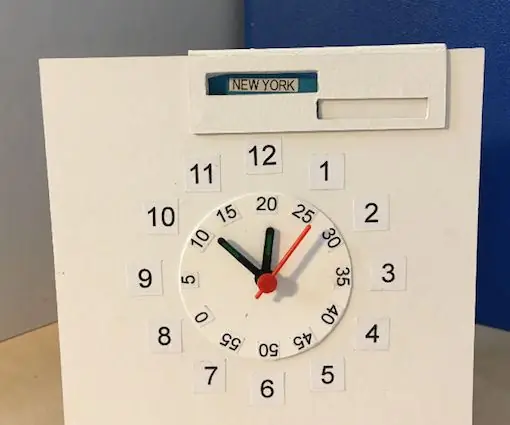

„Универсален“часовник: 10 стъпки (със снимки)

„Универсален“часовник: Този часовник може да показва часа в 24 часови зони по света; това изпълнение се постига благодарение на подредбата, представена на чертежа, показваща основните компоненти на часовника. Часовникът 1 е инсталиран в опората 2, която може да се завърти

Универсален UFC за самолетни симулатори за по -малко от 100 €: 7 стъпки (със снимки)

Универсален UFC за самолетни симулатори за по -малко от 100 €: Когато сте в полетни симулатори, никога нямате достатъчно контролери и бутони. Освен обичайните педали за полет, педали на газта и кормилото, винаги се нуждаете от повече бутони и превключватели, особено с модерни самолети и бойни самолети. Първата ми стъпка беше

24v DC двигател към високоскоростен универсален двигател (30 волта): 3 стъпки

24v DC двигател към високоскоростен универсален двигател (30 волта): Здравейте! В този проект ще ви науча как да преобразувате нормален играчка 24V DC мотор в 30V универсален двигател. Лично аз вярвам, че видео демонстрацията описва най -добре един проект . Така че момчета, бих ви препоръчал първо да изгледате видеото. Проект V

(почти) Универсален MIDI SysEx CC програмист (и секвенсор ): 7 стъпки (със снимки)

(почти) Универсален MIDI SysEx CC програмист (и секвенсор …): В средата на осемдесетте години производителите на синтезатори започнаха „по -малко е по -добре“процес, който доведе до синтезатори barebones. Това позволи намаляване на разходите от страна на производителя, но направи процеса на закърпване достъпен, ако не и невъзможен за крайната употреба

HV9910 Универсален LED драйвер с 220v AC вход: 7 стъпки

HV9910 Универсален LED драйвер с 220v AC вход: HV9910 Universal LED драйвер с 220v AC вход