Съдържание:

- Автор John Day [email protected].

- Public 2024-01-30 07:53.

- Последно модифициран 2025-01-23 14:36.

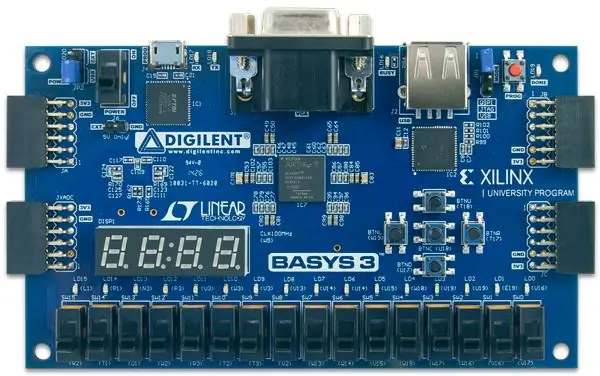

За нашия проект създадохме играта „Mastermind“във VHDL, която да се играе на дъската Basys3. Mastermind е игра за разбиване на кодове, която традиционно се играе с колчета и дъска за игри. Играч един поставя колчета с различни цветове в ред от 4, скрити от играч два. След това играч втори има „х“брой предположения, поставящи колчета на дъската в ред, видим за играч първи. След всяко предположение играч двама се информира за 2 числа: колко от колчетата са с правилния цвят и колко колчета са на правилната позиция в реда. Използвайки тези улики, играч двама трябва да отгатне правилната последователност от щифтове, които играчът първи е поставил в разпределеното число.

В нашето изпълнение играта е за един играч. Програмата генерира произволна комбинация от колчета и играчът трябва да използва дъската Basys3, за да отгатне правилната последователност. Има четири „цвята“, представени с двоични стойности. 7-сегментният дисплей показва три стойности: оставащи завои, брой щифтове в правилната позиция и брой щифтове с правилния цвят в грешна позиция (тези стойности започват от 9, 0 и 0). Играчът използва превключвателите на дъската, за да избере двоичните стойности за своето предположение, и завърта друг ключ, за да изпрати предположението. Ако те са правилни, играта приключва и 7-сегментният дисплей показва „GG“. Ако не, броячът на завои намалява с 1 и играчът получава обратна връзка въз основа на това колко пина в тяхното предположение съответстват на цвета или позицията на щифтовете в комбинацията. Ако играчът се изчерпи, без да се досети правилно, на дисплея се показва „GO“(представляваща играта завърши). Плейърът също може да завърти ключа за нулиране, за да започне отначало по всяко време.

Стъпка 1: Материали

Тъй като цялата игра може да се играе на самата дъска, единствените необходими материали са Basys3 Board, микро USB кабел за свързване към платката и компютър/лаптоп, който можете да използвате за кодиране!

Стъпка 2: Кодът

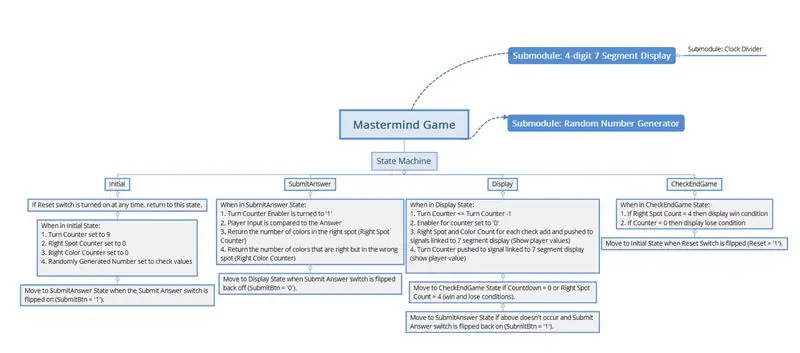

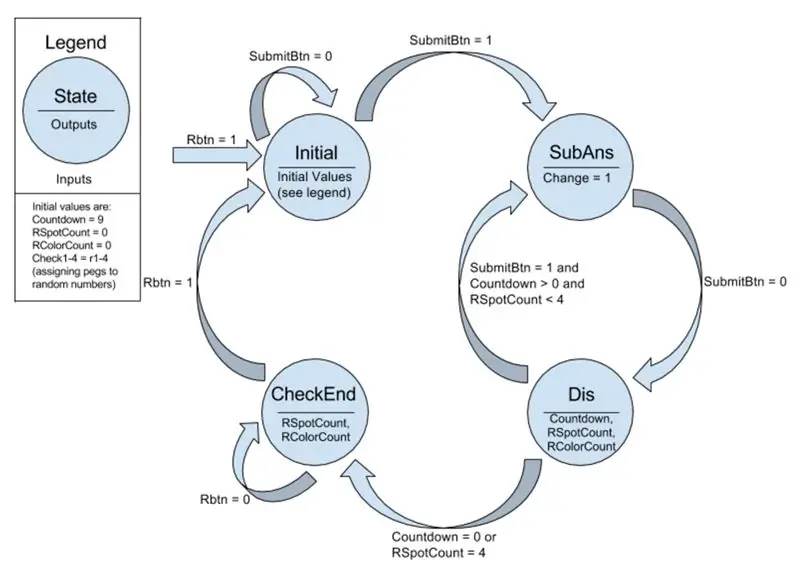

За да може тази игра да работи на FPGA, най -простият начин да я напишете е да създадете държавна машина. Наличието на машина на състоянието позволява последователното и интерактивно преживяване, необходимо за действителната работа на играта. За да може всичко да работи безпроблемно, машината на състоянието ще се основава на вътрешния тактов сигнал на FPGA, като гарантира, че всичко е в синхрон. Основният модул е машина за състояния с четири състояния; Начално състояние (първоначално), състояние на подаване на отговор (подАнсони), състояние на дисплея (Dis) и състояние на CheckEndGame (CheckEnd). Наред с машината на състоянието, основният модул има два подмодула, 4-цифрен седемсегментен дисплей (който има свой собствен подмодул ClkDivider) и генератор на случайни числа (всъщност генератор на псевдо-произволни числа). Съществува и основен технологичен блок, при който светодиодите над всеки превключвател да се включват, когато са включени, като начин хората да виждат по -лесно какво въвеждат. Основен преглед на кода може да се види в представената карта на ума.

Първият компонент за разглеждане е генераторът на случайни числа (randomgen). Тъй като технически не е възможно да се получат истински случайни числа, генерирани от хардуер, най-простото решение беше случайният геен всъщност да бъде регистър за изместване с линейна обратна връзка (LFSR). LFSR има вход на clk и изход „a“(12-битово число). Всеки тактов цикъл се генерира нов 12-битов номер, започващ от „000000000001“, който в крайна сметка преминава през всички комбинации от 12-бита от 1 и 0, преди да се повтори. Изходът „а“се дава на всеки тактов цикъл, така че той работи непрекъснато. Clk е съпоставен с Clk от основния модул, а „a“е съпоставен със сигнала RandNum в основния модул.

Вторият подмодул е 4-цифреният седемсегментен дисплей. Това е доста ясен начин за показване на 4-цифрен седемсегментен дисплей. Дисплеят е настроен на Clk от основния модул, но този подмодул има собствен подмодул на ClkDivider. ClkDivider (настроен на 1298 Hz) се използва за ускоряване на часовника за Седемте сегмента, така че всички цифри да изглеждат включени едновременно (тъй като всъщност само една цифра може да бъде включена наведнъж). Променливата „цифра“се използва за циклично преминаване на петна по дисплея и с всяка цифра идват условията на основен 4-битов входен дисплей, с опции за показване на цифрите от 0 до 9 и също нищо. Най -отдалечената лява цифра на дисплея е зададена на нищо, тъй като не се използва в тази игра.

Основният модул се състои от машината на състоянието. Четирите състояния в процеса са Initial, SubAns, Dis и CheckEnd. Когато е в първоначалното състояние, ако SubmitBtn (превключвателят, използван за изпращане на вашия отговор за проверка) е зададен на „1“, тогава машината се премества в състояние SubAns. По всяко време Rbtn (превключвател, използван за нулиране на машината) е зададен на „1“, след което машината се връща в първоначалното състояние. Когато е в състояние SubAns, когато SubmitBtn = ‘0’ отново, той преминава към състоянието Dis. Когато сте в състояние Dis, ако Обратното броене = 0 (завоите наляво за отгатване падат до 0) или ако RSpotCount = 4 (което означава плейъра като всички правилни цветове в правилните точки), машината отива в състоянието CheckEnd. Ако не се случи нито едно от тях, тогава когато SubmitBtn = ‘1’ отново, той се връща в състояние SubAns, за да позволи друго предположение. Когато сте в състояние CheckEnd, това е краят на играта и единственият изход е да натиснете нулирането, като го върнете в първоначалното състояние. Това може лесно да се види в диаграмата на машината на състоянието. Поведението първоначалното състояние инициализира всичко обратно в изходна позиция. Обратното броене (сигнал, който запазва колко завои наляво има играча) е зададено на 9, RSpotCount (сигнал, който запазва колко от цветовете, които сте предположили, че са на правилното място) е зададен на 0, RColorCount (сигнал, който записва колко от цветовете, за които се досещате, че са правилни, но на грешното място) е зададено на 0, а smallcountdown (сигнал, който в крайна сметка се съпоставя с отброяване, който всъщност променя всеки ход в по -късни състояния) е зададен на 9. Също така, в началното състояние RandNum (генерирано от случайно произволно число) се разделя на четири различни проверки (по една за всеки 3-битов цвят) и се записва в сигнали check1, check2, check3, check4. Тези проверки са това, с което всъщност се сравнява вашето предположение, така че въпреки че LFSR винаги кара RandNum да променя всеки цикъл, след като напуснете първоначалното състояние, проверките остават същите, което позволява запазена стойност да сравнява отговора ви. Това също означава, че всеки път, когато машината се нулира, плейърът има нова стойност за отгатване.

Състоянието SubmitAnswer (SubAns) променя функцията за отброяване (сигнал „промяна“) на „1“. Това е необходимо по -късно, за да работи проследяването на завоите. След това състоянието сравнява входовете на плейъра от превключвателите с проверките, направени в горното състояние. Сигналът rs1, rs2, rs3, rs4 и сигналите rc1, rc2, rc3, rc4 са целочислени типове, които в зависимост от операторите If са зададени на 1 или 0. Сигналът rs е за дясно място и rc за десен цвят. Например, ако предположението на играч с цвят 1 е равно на check1 на RandNum, тогава rs1 = 1, тъй като това означава, че правилния цвят е на правилното място. Ако цвят 1 не е равен на check1, но е равен на една от другите проверки, тогава rc = 1. Това се прави за всеки цвят и всяка проверка.

Състоянието на дисплея (Dis) първо търси средство за отброяване. Ако е „1“, тогава smallcountdown намалява надолу 1 (така че при първия завой става от 9 на 8 и т.н.). В противен случай завоят не се променя. Независимо от това активиране в, всички rs стойности отгоре се добавят и се присвояват на сигнала RSpotCounter. Също така всички rc стойности се добавят и присвояват на RColorCounter. Накрая Countdown се присвоява стойността на smallcountdown. Сигналите RSpotCounter, RColorCounter и Countdown се преобразуват в 4-битови std_logic_vectors извън процеса и се изтласкват към подмодула за показване на седем сегмента чрез карта на портове. По този начин дисплеят показва правилните неща, докато не изпратите нов отговор.

Състоянието на CheckEnd е за това дали сте спечелили или загубили. Ако сте спечелили (всичките 4 цвята са на правилното място, иначе известни като RSpotCounter = 4), тогава „GG“(показано технически като 66) се показва на Седемте сегмента, за да покаже, че сте спечелили. Ако сте загубили (Обратното броене е достигнало 0), тогава „GO“(показано технически като 60) се показва на дисплея за Game Over. И при двата изхода натискането на превключвателя за нулиране в положение включено ще премести машината обратно в първоначалното състояние за възпроизвеждане отново.

Изходният код може да бъде намерен тук.

Стъпка 3: Заключение

Завършването на този проект ни научи много за изграждането на по -сложни схеми. Първоначалният ни дизайн не беше машина с крайно състояние. Затруднявахме се в отстраняването на грешки и пренаписвахме кода няколко пъти, използвайки различни методи (включително FSM). По предложение на инструктора се придържахме към подхода на FSM и успяхме да завършим играта. Научихме, че е много по -ефективно да се проектира кодът въз основа на хардуера, отколкото с традиционния подход за програмиране. Сблъскахме се и с няколко предизвикателства, свързани със седем сегментния дисплей. Да го накараме да показва няколко номера без „призраци“беше трудно и трябваше да използваме часовник за това. Ако трябваше да доразвием този проект, бихме свързали цветни светодиоди към Basys3, така че потребителят да може да вижда цветове (както в традиционната игра), а не цифрови изображения на цветове. В крайна сметка придобихме по -добро разбиране за проектирането на сложни схеми, приложенията в реалния живот и предизвикателствата при използването на хардуер, вместо да изпълняваме симулации с перфектни условия.

Препоръчано:

Проектиране на прост четирипосочен контролер за асоцииран кеш във VHDL: 4 стъпки

Проектиране на прост четирипосочен контролер за асоцииран кеш във VHDL: В предишните ми инструкции видяхме как да проектираме прост директно картографиран кеш контролер. Този път вървим крачка напред. Ще проектираме прост четирипосочен контролер за асоциативен кеш. Предимство? По -малък процент пропуски, но с цената на перфо

Проектиране на програмируем контролер за прекъсвания във VHDL: 4 стъпки

Проектиране на програмируем контролер за прекъсвания във VHDL: Уморен съм от вида на отговорите, които получавам в този блог. Благодаря ви момчета, че посетихте моя блог и ме мотивирахте да споделя знанията си с вас. Този път ще представя дизайна на друг интересен модул, който виждаме във всички SOC - Interrupt C

Проектиране на обикновен кеш контролер във VHDL: 4 стъпки

Дизайн на прост кеш контролер във VHDL: Пиша тази инструкция, защото ми беше малко трудно да получа някакъв референтен VHDL код, за да науча и да започна да проектирам кеш контролер. Затова сам проектирах кеш контролер от нулата и го тествах успешно на FPGA. Имам п

Дизайн на I2C Master във VHDL: 5 стъпки

Дизайн на I2C Master във VHDL: В тази инструкция се обсъжда проектирането на прост I2C master във VHDL. ЗАБЕЛЕЖКА: щракнете върху всяко изображение, за да видите пълното изображение

Проектиране на обикновен VGA контролер във VHDL и Verilog: 5 стъпки

Дизайн на прост VGA контролер във VHDL и Verilog: В тази инструкция ще проектираме прост VGA контролер в RTL. VGA контролер е цифровата схема, предназначена за задвижване на VGA дисплеи. Той чете от Frame Buffer (VGA Memory), който представлява рамката за показване и генерира необходимо