Съдържание:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 07:51.

- Последно модифициран 2025-01-23 14:36.

Потресен съм от отговорите, които получавам в този блог. Благодаря ви момчета, че посетихте моя блог и ме мотивирахте да споделя знанията си с вас. Този път ще представя дизайна на друг интересен модул, който виждаме във всички SOC - Interrupt Controller.

Ще проектираме прост, но мощен програмируем контролер за прекъсвания. Това е напълно конфигуриран и параметризиран дизайн, който е преносим на различни платформи. Проектирах това, след като прочетох много популярни архитектури на контролери за прекъсвания, като NVIC, 8259a, RISC-V PLIC, INTC на Microblaze и др. Надявам се, че момчетата ще ви бъдат полезни и ще ви помогнат да разберете как се обработват прекъсванията от процесор с помощта на контролер за прекъсване.

Стъпка 1: Спецификации

Следват спецификациите на IP:

- AHB3-Lite интерфейс.

-

Статично конфигурируеми параметри:

- Брой външни източници на прекъсвания; поддържа до 63 прекъсвания.

- Брой приоритетни нива; поддържа до 63 нива.

- Брой нива на гнездене; поддържа до 8 нива на гнездене.

- Ширина на шината; 32 или 64.

- Глобално и локално маскируеми прекъсвания.

- Динамично конфигурирано ниво на приоритет за всяко прекъсване.

- Два режима на работа - Напълно вложен режим и Режим с равен приоритет.

- Поддържа чувствителни прекъсвания на високо и високо ниво.

RISC-V PLIC спецификациите, вдъхновени от механизма за ръкостискане, се използват при проектирането.

Прекъсването на прекъсване е вдъхновено от 8259a

Други четения: Microblaze INTC, NVIC

Стъпка 2: Преглед на PIC

Програмируем контролер за прекъсвания (PIC) получава множество прекъсвания от външни периферни устройства и ги обединява в един изход за прекъсване към ядрото на целевия процесор.

PIC се контролира чрез контролни и статусни регистри. Всички PIC регистри са картографирани в паметта и са достъпни чрез интерфейса на шината AHB3-Lite.

Регистърната банка се състои от регистър за конфигуриране, регистри за разрешаване, чакащи регистри, регистрирани в експлоатация, приоритетни регистри и идентификационен регистър, които са типични за контролерите за прекъсвания.

Конфигурационният регистър се използва за задаване на режима на работа на PIC. Той може да работи както в напълно вложен режим, така и в режим на равен приоритет.

На всяко прекъсване могат да бъдат зададени приоритети и индивидуално маскирани. Поддържа се и глобално маскиране на всички прекъсвания.

Банката на регистрите взаимодейства с Приоритетния резолвер и BTC (Binary-Tree-Comparator), за да разреши приоритетите на чакащите прекъсвания и съответно да потвърди прекъсването на процесора. Идентификационният регистър съдържа идентификатора на най -висок приоритет, който чака прекъсване.

Стъпка 3: Проектиране и внедряване на RTL

Дизайнът на PIC е насочен към намаляване на латентността при разрешаване на приоритетите, което е най -критичната за времето част от дизайна. Тъй като дизайнът решава приоритетите в един тактов цикъл, производителността се влошава с увеличаването на броя на източниците със сложност на Log2.

Дизайнът е успешно реализиран и времето е проверено до следните честоти на FPGA на Artix-7.

- До 15 източника: 100 MHz

- До 63 източника: 50 MHz

Латентността на прекъсване, добавена само от PIC, е 3 тактови цикъла (с изключение на времето за превключване на контекста на процесора и първото време за извличане на инструкция ISR).

Стъпка 4: Важни бележки и прикачени файлове

Важни бележки:

- Ако интерфейсът на AHB3-Lite е нежелан, можете да промените горния модул и да използвате скелетния дизайн на PIC. Предоставеният тестов стенд обаче е за IP с AHB3-Lite интерфейс.

- PIC IP v1.0 е напълно преносим, гол RTL дизайн.

- Функционално проверен за работа и в двата режима.

Прикачени файлове:

- Кодове за проектиране и тестове във VHDL.

- Пълна IP документация.

Това е дизайн с отворен код … Чувствайте се свободни да използвате …

За всякакви запитвания, по всяко време:

Миту Радж

Препоръчано:

Лаборатория за прекъсвания (незавършена работа): 3 стъпки

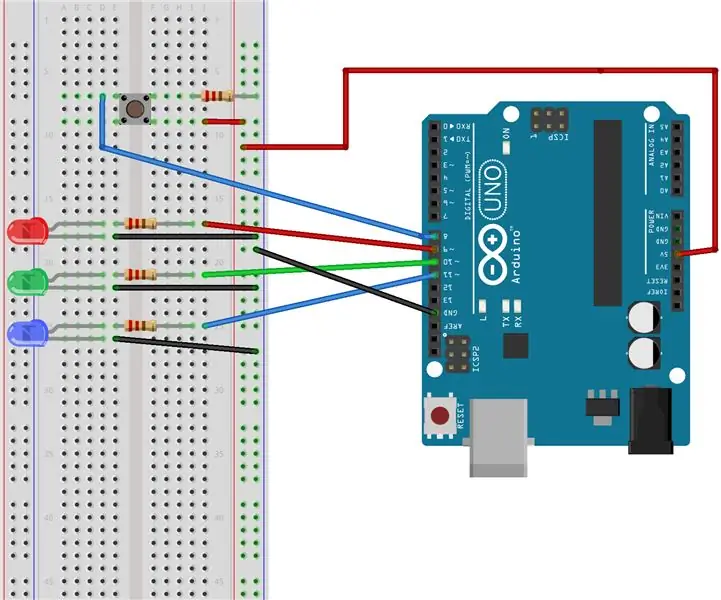

Лаборатория за прекъсвания (незавършена работа): Целта на тази лаборатория е да стартира програма Arduino, използваща прекъсвания. Тази лаборатория не работи напълно правилно поради проблеми с кодирането. Какво ще ви е необходимо:- 1 Arduino Uno- 1 Макетна платка- 1 бутон- 3 светодиода- 220 ома резистори- Джъмперни проводници

Проектиране на прост четирипосочен контролер за асоцииран кеш във VHDL: 4 стъпки

Проектиране на прост четирипосочен контролер за асоцииран кеш във VHDL: В предишните ми инструкции видяхме как да проектираме прост директно картографиран кеш контролер. Този път вървим крачка напред. Ще проектираме прост четирипосочен контролер за асоциативен кеш. Предимство? По -малък процент пропуски, но с цената на перфо

Проектиране на обикновен кеш контролер във VHDL: 4 стъпки

Дизайн на прост кеш контролер във VHDL: Пиша тази инструкция, защото ми беше малко трудно да получа някакъв референтен VHDL код, за да науча и да започна да проектирам кеш контролер. Затова сам проектирах кеш контролер от нулата и го тествах успешно на FPGA. Имам п

Проектиране на обикновен VGA контролер във VHDL и Verilog: 5 стъпки

Дизайн на прост VGA контролер във VHDL и Verilog: В тази инструкция ще проектираме прост VGA контролер в RTL. VGA контролер е цифровата схема, предназначена за задвижване на VGA дисплеи. Той чете от Frame Buffer (VGA Memory), който представлява рамката за показване и генерира необходимо

Проектиране на UART във VHDL: 5 стъпки

Дизайн на UART във VHDL: UART означава универсален асинхронен приемник предавател. Това е най -популярният и най -прост протокол за серийна комуникация. В тази инструкция ще научите как да проектирате UART модул във VHDL