Съдържание:

- Автор John Day [email protected].

- Public 2024-01-30 07:52.

- Последно модифициран 2025-01-23 14:36.

Знам какво мислите: "А? Има много инструкции за това как да се използват микроконтролери за измерване на честотата на сигнала. Прозяване." Но изчакайте, в това има новост: описвам метод за измерване на честоти, много по -високи от тези, които микроконтролерът (MCU) може да понесе, и работния цикъл на сигнала - всички едновременно!

Честотният диапазон на устройството обхваща от ~ 43 Hz до ~ 450 kHz, докато работният цикъл варира от 1% до 99%.

Позволете ми да обясня частта "може да понесе": MCU измерва периода на сигнал с квадратна вълна, T, като проследява времето между две последващи преходни събития. Например, ниско до високо напрежение скача върху един от своите I/O щифтове. Той го прави, като брои броя на импулсите на собствения си вътрешен часовник. Наивно горната граница за измерените честоти трябва да се подчинява на теоремата за вземане на проби от Nyqvist-Shannon; т.е. това би било приблизително равно на половината от тактовата честота на MCU. В действителност границата е много, много по -ниска, защото MCU трябва да изпълнява код за обработка на прекъсвания, запазване на променливи, извършване на аритметични операции, показване на резултати и т.н. В моите експерименти с 48 MHz MCU минималният брой тактови цикли между измеримите преходи беше около 106. Следователно горната граница на измеримия честотен диапазон в този случай би била 48 000 /212 /2 = 226,4 kHz.

Докато MCU измерва периода на сигнала, той може също да определи неговата ширина на импулса, P: времето на оставащото високо напрежение на сигнала. С други думи, време между ниски към високи и високи към ниски преходи. Работният цикъл на сигнала след това се определя като следния процент:

Задължение = 100% * P / T

Точно както в случая на честотата, има практическо ограничение за ширината на импулса. Използвайки горния пример, 106 тактови цикъла биха ограничили ширината на импулса до не по -малко от 2,21 микросекунди. Или не по -малко от 50% при 226,4 kHz.

Един от начините за увеличаване на горната честотна граница на сигналите с квадратна вълна е прилагането на цифрови разделители, които използват джапанки. Разделянето на входната честота на n би разширило измеримия горен диапазон n пъти. Това е страхотна новина, цифровите разделители имат един основен недостатък: разделеният сигнал губи информацията за ширината на импулса (и работния цикъл)! Поради начина на работа на разделителите, тяхната продукция винаги има 50% работен цикъл. Грозно…

На следващите страници обаче ще покажа как да разделя цифрово честотата и да запазя първоначалната ширина на импулса, което ми позволява да измервам сигнали много извън границите, наложени от директното броене.

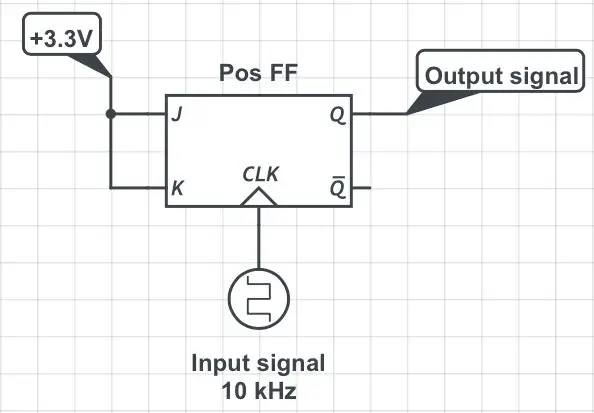

Стъпка 1: Цифрово разделение на честотите

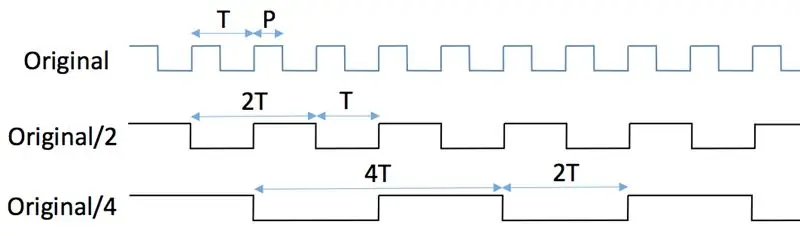

Традиционните цифрови честотни разделители използват джапанки; този урок добре обяснява принципите как да се конструират разделители, използвайки стандартни джапанки JK. Това решава проблема с твърде високи входни честоти за MCU, но има един основен недостатък: разделеният сигнал има 50% работен цикъл, независимо от натоварването на входния сигнал! За да разберете защо е така, погледнете първите две фигури. Оригиналният сигнал с период T и ширина на импулса P се подава в тактовия щифт на JK тригер, докато неговите J и K щифтове се държат високи по всяко време (първа фигура). 3.3V логика се приема навсякъде. Да предположим, че джапанката се задейства от положителния (т.е. нарастващ) ръб на часовника. При тези условия, промените в състоянието на изходния щифт (отделни „флипове“и „флопове“) се случват всеки път, когато щифтът на часовника премине от ниско към високо. Преходът от висок към нисък часовник (т.е. отрицателният ръб) се игнорира напълно. Вижте втората фигура. Изходният щифт Q излъчва сигнал, чийто период е два пъти по -дълъг от първоначалния период, т.е.честотата му се намалява наполовина. Ширината на импулса на изхода винаги е равна на T. Следователно първоначалната ширина на импулса, P, се губи.

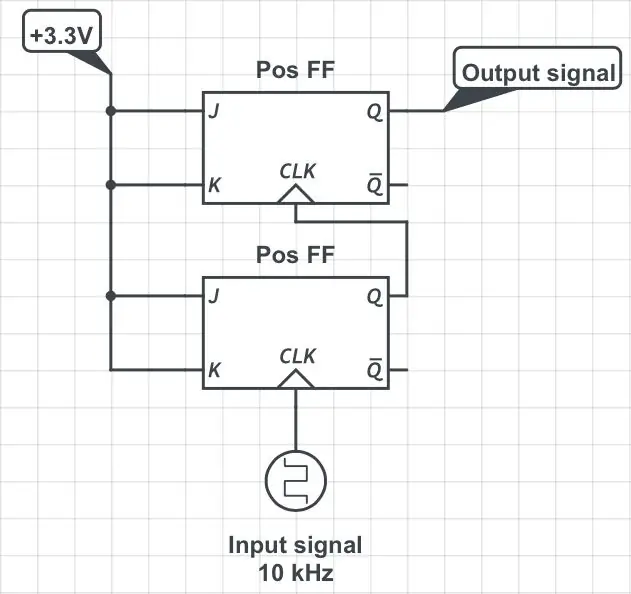

Добавянето на друг JK тригер в конфигурация, показана на третата фигура, разделя първоначалната честота на 4. Добавянето на още джапанки по същия последователен начин разделя честотата на последващи степени 2: 8, 16, 32 и т.н.

Проблем: как да се раздели честотата на квадратна вълна, като същевременно се запази нейната ширина на импулса?

Идеята е правилно да се добави JK тригер с отрицателен ръб, задействан. Нека го наречем "Neg FF"; вижте четвъртата фигура. Тук "правилно" означава, че J и K щифтовете на новия тригер са обвързани съответно с изходните щифтове Q и Qbar на разделителя по 4 ("Pos FF"), илюстрирани на предишната фигура. (Тук "bar" е хоризонталната лента над символа Q, показваща логическо отрицание.) За да видите какво постига това, погледнете таблицата с функции на "Neg FF" на петата фигура: изходните щифтове на Neg, Q и Qbar, отразяват състоянието на своите входни щифтове, J и K, съответно. Което означава, че те отразяват състоянието на Pos 'Q и Qbar. Но действието на тригера на Neg трябва да изчака отрицателния ръб на първоначалния сигнал, който пристига в момент P след положителния ръб. Аха!

Получените форми на вълните са илюстрирани на шестата фигура. "Pos Q" извежда сигнал на 1/4 -та честота, "Pos Qbar" е обратен, "Neg Q" следва "Pos Q", изместен от ширината на импулса P, а "Neg Qbar" е неговата обратна. Можете да проверите, че логическото И на "Pos Qbar" и "Neg Q" произвежда импулсен ход, характеризиращ се с оригиналната ширина на импулса P и 1/4 от честотата. Бинго!

Първоначално използвах точно този изходен сигнал за захранване на MCU. Обаче се оказа проблем за много кратки импулсни дължини поради ограничението на 106 цикъла на MCU, споменато във Въведението. Реших този малък проблем, като избрах друг изход: „Pos Qbar“И „Neg Qbar“вместо това. Един поглед към вълновите форми трябва да ви убеди, че ширината на импулса на тази конкретна форма на вълната, P ', варира между T и 2T вместо (0, T) диапазон за P. P може лесно да бъде възстановен от P' чрез:

P = 2T - P '

Стъпка 2: Препоръчителен хардуер

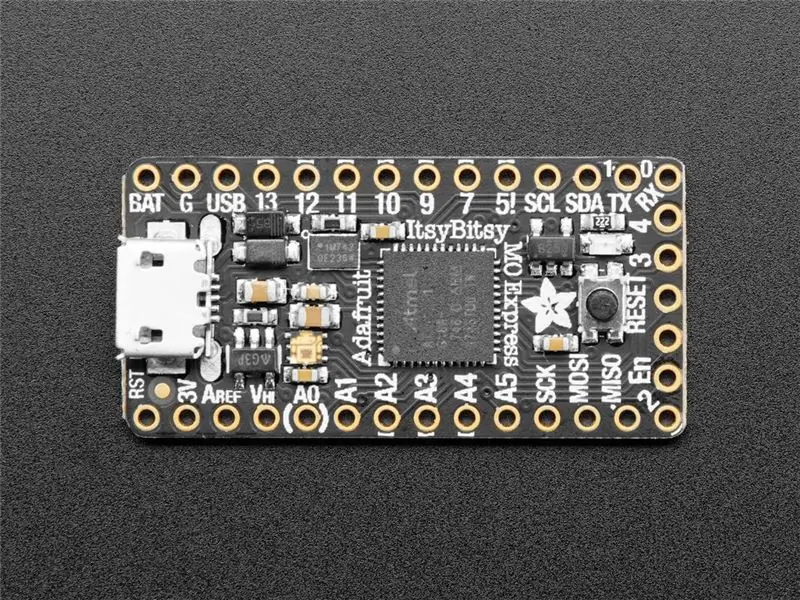

Наистина харесвам сравнително новодошлия на електронните любители: Atmel SAM D21 MCU, базирани на 32-битов ARM Cortex M0+ процесор, работещ с тактова честота 48 MHz, много по-висока от по-старите Atmels. За този проект купих:

- MCy платка ItsyBitsy M0 Express от Adafruit

- Случайно имах акумулаторна LiPo батерия от Adafruit

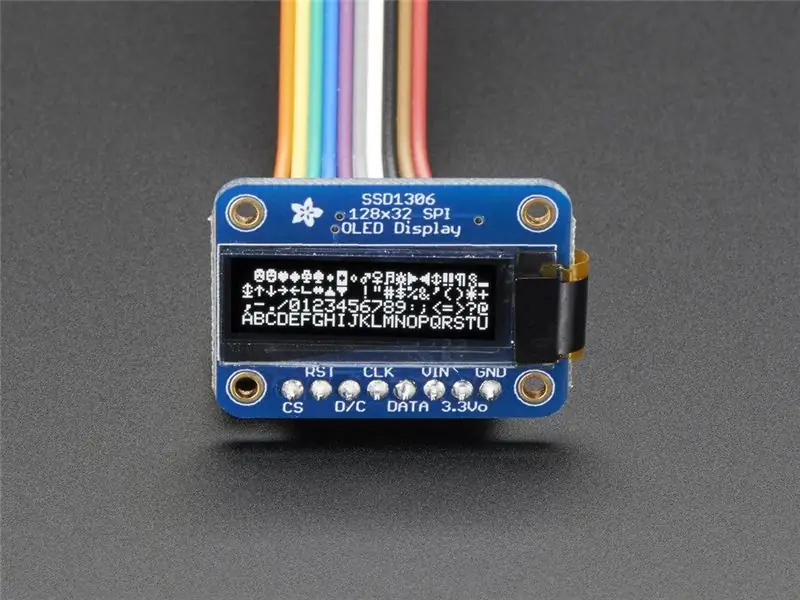

- Монохромен 128x32 SPI OLED дисплей (познахте: Adafruit)

- Двойно джапанка JK, задействана с положителен ръб SN74HC109 от Texas Instruments

- Двойно тригер JK тригер с отрицателен ръб SN74HC112 от Texas Instruments

- Четворна и порта CD74AC08E от Texas Instruments

- Четворна или порта CD74AC32E от Texas Instruments

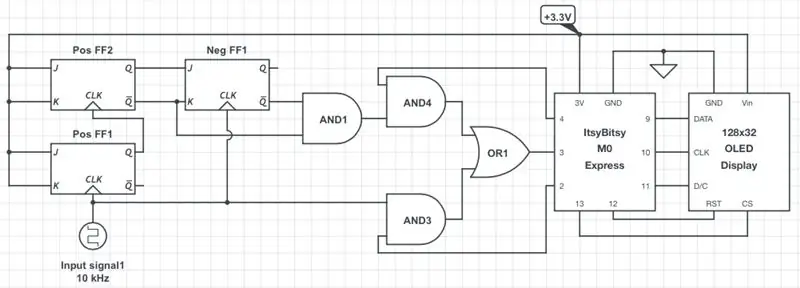

Стъпка 3: Веригата

Първата фигура показва опростена схема на измервателя на честота/натоварване. Логиката на 3.3 V CMOS се приема навсякъде. Следователно амплитудата на входната квадратна вълна трябва да бъде между съответния VIH ниво (т.е. 2 V) и 3,3 V. Ако не, трябва съответно да го увеличите или намалите. В повечето случаи обикновен делител на напрежение би бил достатъчен. Ако искате да проектирате вашата версия на глюкомера на различно логическо ниво, тогава трябва да използвате друг микроконтролер (MCU), батерия и дисплей, които работят на желаното ниво. Логическите порти и джапанки, използвани в този проект, работят с логически нива навсякъде между 2 V и 6 V и в повечето случаи трябва да са ОК.

Както е показано, MCU на ItyBitsy използва щифтове 9-13 за комуникация с дисплея чрез софтуерния SPI протокол. 3V щифтът осигурява захранване на цялата верига. Пин 3 на цифровия вход приема анализирания сигнал, докато пинове 2 и 4 контролират източника на сигнала: или директен сигнал, идващ през порта AND3 (ниски входни честоти), или сигнал, разделен на 4 през порта AND4 (високи входни честоти), както е описано в Стъпка 2 Кодът, обсъден в следващата стъпка, автоматично открива входящия честотен диапазон и по подходящ начин превключва източника на сигнал.

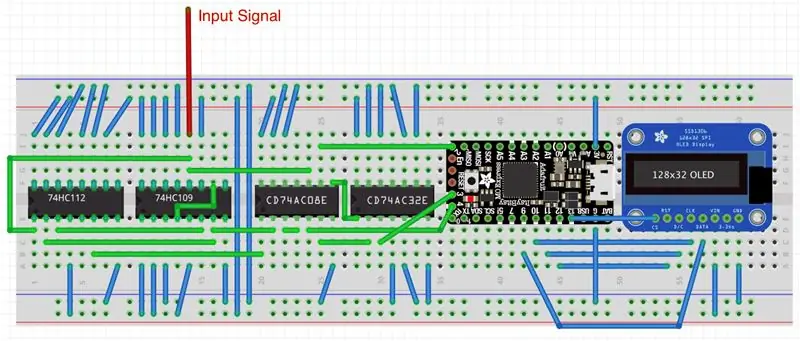

Схемата не показва истинската сложност на цифровите чип връзки. Второто изображение показва как би изглеждал проектът на макет. Входният сигнал идва през червен проводник към щифта 2CLK на двойния тригер с положителен ръб. ВНИМАНИЕ: Обикновено всички J и K щифтове на този джапанки трябва да се държат високо, но SN74HC109 по -специално разполага с Kbar щифт - обърнат K щифт - вместо това. Следователно този щифт трябва да бъде заземен! Първият тригер с отрицателен ръб в SN74HC112 има своя 1K и 1J щифт, свързан към 1Q и 1Qbar щифтовете на SN74HC109. Вторият тригер в SN74HC112 не се използва и неговите входни щифтове (2K, 2J, 2CLRbar) са заземени. Всички други допълнителни пинове PREbar (предварително зададени) и CLRbar (изчистени) във всички джапанки трябва да бъдат свързани към логически висок. Неизползваните пинове за часовник и изход остават несвързани. По същия начин неизползваните входни щифтове във всички врати са заземени, докато неизползваните изходни щифтове се оставят несвързани. Както обсъдих в моя "Невидим убиец на телефонния звънец", заземяването на неизползвани входни щифтове на логически чипове елиминира случайни трептения и спестява енергия на батерията.

Стъпка 4: Кодът и измерването на ниски честоти

Естествено, всички действия се извършват в кода, свързан по -долу. Когато входящият вход на щифт 3 се превключи от цифров нисък към висок, MCU започва да брои импулсите на своя вътрешен такт от 48 MHz. Той отбелязва момента на преход от високо към ниско и продължава броенето до следващото превключване от ниско към високо, когато рестартира отново целия процес. Първият брой представлява ширината на импулса, докато целият брой представлява периода на сигнала. И това е цялата тайна.

Процесорът отбелязва тези преходи чрез хардуерни прекъсвания. SAMD21 има няколко часовника; моят код използва TC3 one. Първоначално започнах, като прочетох листа с данни на M0, който се вдига за много усилия при кодирането на манипулатора на прекъсвания, но скоро открих много свързан код в публикациите на Arduino Forum от потребители electro_95, MartinL и Rucus, чийто принос е надлежно признат. Включих и модифицирах техния комбиниран код в моя; спестявайки ми много време!

Както споменах по -рано, разделителната способност на сигнала е ограничена от ~ 106 цикъла на процесора за изпълнение на код между прекъсвания. Цифровото разделение със запазване на ширината на импулса се грижи за високите честоти. Ниските честоти, от друга страна, представляват друго предизвикателство: тъй като броячът на часовника на TC3 е дълъг 16 бита, той прелива, след като премине границата от 65, 536 броя. Човек може да се справи с тази ситуация, като добави прекъсване на препълване, но избра различно решение: TC3 може да използва предварително мащабиран (т.е. софтуерно разделен) часовник на процесора вместо хардуерния 48 MHz. По този начин, ако периодът на сигнала се доближи до границата на препълване, кодът може да инструктира TC3 да използва 24 MHz броя за следващия период и, ето, броячът пада под 32, 768 броя. За още по -ниски честоти TC3 може да бъде инструктиран да отчита 12 MHz импулси и др. Подходящият предварително делител се определя автоматично въз основа на честотата на сигнала, с хистерезис, за да се поддържа броячът на TC3 в границите на препълване. В резултат на това долният край на обхвата на устройството е около 43 Hz.

Можете да раздвоите кода и да го използвате във вашия проект, но моля, споменете неговия източник, когато публикувате резултати.

Връзка към кода.

Препоръчано:

Attiny85 Едновременно програмиране или тиква с многоцветни очи: 7 стъпки

Едновременно програмиране на Attiny85 или тиква с многоцветни очи: Този проект показва как да управлявате два 10-милиметрови трицветни общи анодни светодиода (многоцветни очи на Pumpkin Halloween Glitter) с чип Attiny85. Целта на проекта е да запознае читателя с изкуството на едновременното програмиране и с използването на Adam D

Как да си направим CubeSat, който може да измерва температурата: 3 стъпки

Как да си направим куб Сът, който може да измерва температурата: Елате и ще видите куб 11x11x11x11 чисто въображение, вземете ме за ръка и ще видите температурата на Марс! (в мелодията на „Въображението“на Уили Уонка) Днес ще ви покажа, че трябва да изградите свой собствен CubeSat! Аз и моите партньори Алиса и

Как да си направим дрон с Arduino UNO - Направете квадрокоптер с помощта на микроконтролер: 8 стъпки (със снимки)

Как да си направим дрон с Arduino UNO | Направете квадрокоптер с помощта на микроконтролер: Въведение Посетете канала ми в Youtube Drone е много скъпа притурка (продукт) за закупуване. В този пост ще обсъдя как да го направя евтино ?? И как можете да си направите такъв на ниска цена … Е, в Индия всички материали (двигатели, ESC

Автоматично изпращане на имейл със снимка от пакетния файл с помощта на стария работен плот и XP: 4 стъпки

Автоматично изпращане на имейл със снимка от пакетния файл с помощта на стария работен плот и XP: Имам голям късмет да имам страхотна гледка от прозореца на домашния си офис. Когато съм далеч, искам да видя какво ми липсва и често съм далеч. Преди имах собствен уебсайт и домашна метеорологична станция, която да качва чрез ftp цялото време

Как да броим от 0 до 99 с помощта на 8051 микроконтролер със 7 сегментен дисплей: 5 стъпки (със снимки)

Как да броим от 0 до 99 с помощта на 8051 микроконтролер със 7 -сегментен дисплей: Здравейте на всички, В този урок ще ви разкажем как да броите от 0 до 99, като използвате два 7 -сегментни дисплея