Съдържание:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 07:51.

- Последно модифициран 2025-01-23 12:57.

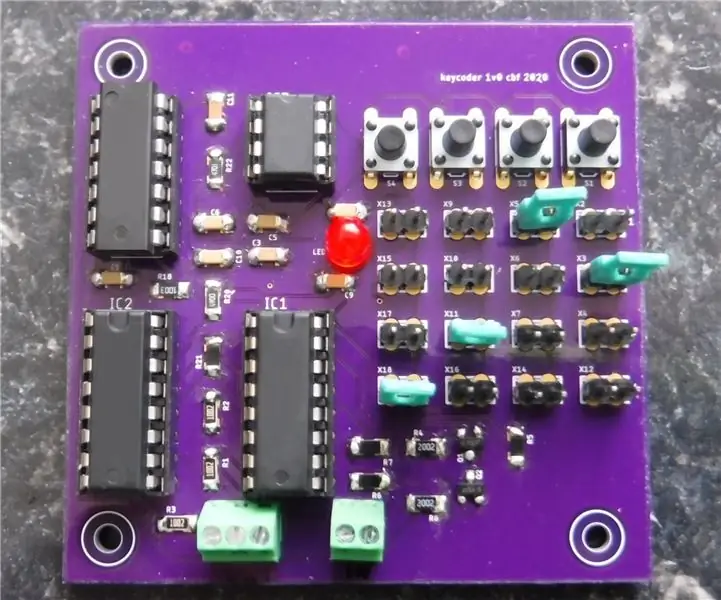

Това е прост програмируем код с 4 бутона.

интерфейсен модул и като такъв може да се използва в редица проекти, при които може да се наложи управление без ключа без ключа. Показана е само печатната платка за генериране на необходимия сигнал за иницииране на заключващ механизъм, заключващият механизъм е оставен на потребителя.

Печатната платка използва комбинация от компоненти за повърхностно монтиране и отвори с отвори, които са всички лесно достъпни, за да се монтират SMT компонентите ще са необходими стабилна ръка и спойка с фин връх. За по -лесна конструкция DIP са монтирани в гнезда. Винтовите клеми се използват за свързване на 9V батерия (5V min до 15V max) и изход.

Създадох оформлението на печатни платки с помощта на Eagle Cad и това беше произведено в OSH Park.

Консумативи

Списък на компонентите

3 × 10k резистор 1206

2 × 20k резистор 1206

4 × ПЕРЕКЛЮЧВАТЕЛ SPST-NO

1 × 3 Way терминален блок на печатни платки 2,54 мм стъпка

1 × 2 Way терминален блок на печатни платки 2,54 мм стъпка

2 × 16 пинов IC гнездо по избор

1 × 14 -пинов IC гнездо по избор

1 × 8 -пинов IC гнездо по избор

1 × PCB двуслойна дъска

2 × 47k резистор 1206

1 × 10n кондензатор 1206

1 × 100n кондензатор 1206

2 × BSS123 NFET SOT23

2 × CD4027 Двоен джапанка JF 16DIP

1 × CD4081 Quad 2 вход И 14DIP

1 × 555 Таймер 8DIP

1 × LED ЧЕРВЕН 3 мм

16x клемни щифтове 2,54 мм разстояние

Стъпка 1: Описание на веригата

Схемата се реализира с помощта на CMOS логически порти, таймер чип и шепа дискретни компоненти.

Централният елемент е джапанката JK, от която се използват четири, това изисква CD4027, който съдържа две джапанки, поради което са необходими две от тях.

CD4027 се предлага с 16 пина в DIP и SMD, изходът и функционалността са еднакви, независимо от пакета.

Таблицата на истината показва състоянието на работа.

LH = Преход от нисък към висок, HL = Преход от висок към нисък, NC = Без промяна, X = Не ми пука.

За това приложение S и R входовете са ниски, поради което в този случай последните три реда от таблицата на истината могат да бъдат игнорирани.

Следователно, изходното състояние на джапанката (FF), ще се определя от високото ниво на входа J или K, когато часовникът (CLK) е на нарастващия ръб (LH).

Всеки от първите три клавиша на клавиатурата е свързан към входа J на FF, който открива състоянието на клавиша, като натиснат клавишът не е натиснат, входът е нисък (по подразбиране се дърпа ниско от резистор), когато клавишът е натиснат J входът се повишава, когато CLK промени LH. Причините за увеличаване на Q изхода.

Вторият FF се затваря чрез комбинация от състоянието на предишния 1 -ви FF и CLK чрез порта AND.

CD4081 quad 2 вход AND се предлага с 14 пина в DIP и SMD, изходът и функционалността са еднакви, независимо от пакета

Ако изходът на първия FF е висок, изходът на втория FF ще се повиши, когато часовникът е натиснат, когато е натиснат вторият клавиш.

Третият FF е затворен от втора AND порта (чрез изхода на втората FF) и CLK.

K входовете на всички FF са свързани заедно чрез четвъртия клавиш, натискането на това осигурява високо ниво, което на следващата LH на входната CLK принуждава Q изходите да са ниски и нулира всички FF. Ако бутонът не е натиснат, входът е задържан ниско (по подразбиране се дърпа ниско от резистор).

В допълнение към ръчното нулиране, осигурено от четвъртия клавиш, захранването при нулиране (POR) се осигурява от кондензатора/резистора (CR), мрежата, образувана от кондензатора през превключвател 4 и падащия резистор на K входовете.

Когато се подаде захранване, CR мрежата осигурява HL импулс към K входовете и с J входовете, издърпани ниско от резистор (J = L, K = H), всички Q изходи са ниски.

Изходът на 3 -ти FF е свързан към един вход на 2 входен EXOR, другият вход е свързан към POR мрежа.

Налични са EXOR с единична порта, но максималното им работно напрежение е 5.5V, което е в долния край на CMOS работното напрежение. Във всеки случай намерението е да се задейства веригата при 9V

За тази цел беше създаден EXOR, използващ резистори, NFET и 3 -ти порта AND.

Изходът на портата EXOR CLK през 4 -та порта AND към входа на 4 -ти FF беше J = H и K = LH превключва изхода на FF. Когато Q = L заключването е настроено, когато Q = H заключването не е настроено.

Часовникът се генерира с помощта на таймер 555, конфигуриран в режим Astable.

Стъпка 2: Монтаж

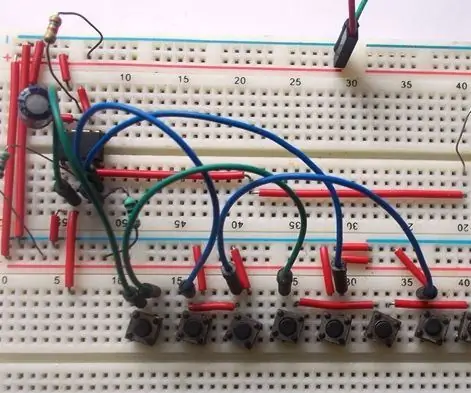

Първо прикрепете устройствата за повърхностен монтаж, това предотвратява блокирането на тези компоненти от по -големите компоненти през отворите и на този етап дъската е плоска, което опростява сглобяването.

След това запоявайте IC гнездата, освен ако не монтирате IC директно към платката.

IC гнездата обаче могат да опростят отстраняването на грешки и подмяната в случай на проблеми.

Поставете клемните щифтове, освен ако не прибягвате до телени връзки.

Клемните блокове са последни за запояване, тъй като седят по -високо от другите компоненти.

Стъпка 3: Операция

Условието дали устройството е настроено или изключено е посочено със светодиод, което може да бъде разширено над или отдалечено от основната платка според изискванията.

Светодиодът остава включен, когато е настроен. (също по подразбиране при включване).

Настройването и премахването на настройките се осъществява чрез въвеждане на комбинация от 4 бутона, правилният код включва светодиода, което показва, че системата е настроена, а правилният код изключва светодиода.

Неправилна кодова последователност прилага нулиране към системата, като изисква кодовата последователност да бъде въведена отново от самото начало.

Изискваният код се задава от джъмпери (позволяващи лесно промяна на кода) или връзки (твърдо кодирани, по -малко гъвкави).

Твърдото кодиране отрича терминалните стойки, опростявайки конструкцията, но прави промяната на кода по -малко удобна

Връзките са подредени в групи по две в матрица 4 x 4.

Колоната се подравнява със съответния превключвател, по една колона на превключвател.

Редът се подравнява с реда на превключване от 1 до 4.

Като пример S1.

Под S1 има 4 връзки в съответната колона.

Ако втората връзка е направена, тя присвоява S1 като втори бутон в последователността и т.н.

Същата методология е приложима за всички бутони.

Стъпка 4: Отстраняване на неизправности

Могат да възникнат проблеми и ако се появят, как могат да бъдат решени.

Първото нещо, което трябва да направите, е да потърсите очевидното.

IC на погрешно място, неправилна ориентация или щифт (и) не са запоени или слабо запоени, лошо поставяне на гнездо или огънат щифт.

Компонент в неправилно положение, грешна стойност, неправилна ориентация или лошо запояване.

Спояване на спойка, Захранващо напрежение на грешните клеми, захранващи проводници сменени, неправилно напрежение.

Дори печатната платка може да има отворена или къса песен (и)

Не си казвайте, че не може да е конкретен проблем, без да го проверите

Препоръчано:

Електронно коледно дърво: 4 стъпки

Електронно коледно дърво: Здравейте! Бих искал да представя моето електронно коледно дърво. Изградих това като декорация и мисля, че е много съчетано и хубаво

Black Lives Matter Електронно превъртане на имена Знак: 5 стъпки

Black Lives Matter Electronic Scrolling Names Sign: Кампаниите #sayhername, #sayhisname и #saytheirname информират за имената и историите на чернокожи хора, които са станали жертва на расистко полицейско насилие и насърчава застъпничеството за расова справедливост. Повече информация за исканията и

Как да направите безопасно заключване с RFID заключване: 5 стъпки

Как да направите безопасно заключване с RFID заключване: Научете как да направите безопасно заключване с RFID заключване у дома, използвайки Arduino и много основни електронни компоненти. Нека направим безопасно шкафче с RFID заключване, използвайки Arduino и Rfid скенер

Електронно кодово заключване: 4 стъпки

Електронно кодово заключване: Цифровите кодови ключалки са много популярни в електрониката, където трябва да въведете определен „код“, за да отворите ключалката. Този тип ключалки се нуждаят от микроконтролер, за да сравнят въведения код с предварително дефинирания код, за да отворят ключалката. Има такива видове

Електронно RFID заключване на вратата: 9 стъпки

Електронна ключалка за RFID врати: Днес ще ви науча как проектирам и изграждам " КРАЙНА ЕЛЕКТРОННА ЗАКЛЮЧВАНЕ НА ВРАТИ " следвайте ме в този урок стъпка по стъпка, ще ви обясня всеки детайл и проблеми, които имах по време на строителството. Надявам се да ви хареса! Както можете да видите в