Съдържание:

- Стъпка 1: Изграждане на PWM модул- изходен файл

- Стъпка 2: Изграждане на PWM модул- настройка на Vivado

- Стъпка 3: Изграждане на PWM модул- Създайте проект файл

- Стъпка 4: Изграждане на PWM модул- Дизайн на блок и настройка на файл за ограничения (I)

- Стъпка 5: Изграждане на PWM модул- Дизайн на блок и настройка на файл за ограничения (II)

- Стъпка 6: Изграждане на ШИМ модул- Дизайн на блок и настройка на файл за ограничения (III)

- Стъпка 7: Изграждане на PWM модул- Дизайн на блок и настройка на файл за ограничения (IV)

- Стъпка 8: Изграждане на PWM модул- Дизайн на блок и настройка на файл за ограничения (V)

- Стъпка 9: Изграждане на PWM модул- инсталиране на хардуер

- Стъпка 10: Изграждане на PWM модул- Генериране на битстрийм и стартиране на SDK

- Стъпка 11: Изграждане на PWM модул- Създайте ново приложение в Xilinx SDK

- Стъпка 12: Изграждане на PWM модул- преглед на Project Explorer (I)

- Стъпка 13: Изграждане на PWM модул- преглед на Project Explorer (II)

- Стъпка 14: Изграждане на PWM модул- Преглед на Project Explorer (III)

- Стъпка 15: Изграждане на PWM модул- приключване на PWM функция (I)

- Стъпка 16: Изграждане на PWM модул- приключване на PWM функция (II)

- Стъпка 17: Изграждане на PWM модул- приключване на PWM функция (III)

- Стъпка 18: Изграждане на PWM модул- Накарайте го да работи

- Стъпка 19: Обработка на поточно видео на Digilent ZYBO с OV7670

- Стъпка 20: Пълна блокова диаграма

- Стъпка 21: Свържете OV7670 към ZYBO

- Стъпка 22: Създайте дизайн на блок

- Стъпка 23: Добавете VHDL файлове за управление и заснемане на камера OV7670

- Стъпка 24: Добавете файл с ограничения

- Стъпка 25: Добавете IP Repo за HLS IP

- Стъпка 26: Добавете модули и IP

- Стъпка 27: Настройки за IP конфигурация

- Стъпка 28: Добавете и конфигурирайте PS IP блок

- Стъпка 29: Част 1. Изграждане на ШИМ модул за серво мотори

- Стъпка 30: Видеовходни странични връзки (aclk подчертано)

- Стъпка 31: Връзки с OV7670

- Стъпка 32: Връзки от външната страна на видеото

- Стъпка 33: Изпълнете автоматизация на блокиране и свързване

- Стъпка 34: Генерирайте HDL Wrapper

- Стъпка 35: Генерирайте Bitstream, експортирайте хардуера в SDK, стартирайте SDK от Vivado

- Стъпка 36: SDK (без FreeRTOS)

- Стъпка 37: Изпълнение на FreeRTOS

- Стъпка 38: Инструкции за употреба

- Стъпка 39: Препратки и връзки

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 07:54.

- Последно модифициран 2025-01-23 14:36.

Започнете от първа стъпка за подробности относно създаването на двуосен серво ШИМ контролер.

Започнете от масивната блокова диаграма (Стъпка 19) за пълния проект.

Настройка за камера + панорама/накланяне, която използвахме:

PmodCON3 от Digilent беше използван за свързване на сервомоторите.

Стъпка 1: Изграждане на PWM модул- изходен файл

Стъпка 2: Изграждане на PWM модул- настройка на Vivado

Първо изтеглете Vivado Design Suite от уебсайта на Xilinx. Инсталирайте целия пакет за проектиране, включително Vivado Software Development Kit (SDK). Този проект използва версия 2017.2.

Междувременно Digilent Adept 2 също трябва да бъде инсталиран като драйвер за платка Zybo.

Стъпка 3: Изграждане на PWM модул- Създайте проект файл

Преди да създадете файл на проект, трябва да се уверите, че вече сте инсталирали правилно файла Zybo като урок тук:

Vivado версия 2015.1 и по -нова инсталация на файлове на борда

Отворете Vivado 2017.2. При Бърз старт щракнете върху Създаване на проект -> Напред -> Име на проект (Име на името на вашия проект тук) -> Тип на проекта. В Тип проект изберете RTL Project и маркирайте „Не посочвайте източници в момента“. След това за частта по подразбиране изберете „дъски“и „Zybo“като показвано име. След това щракнете върху Готово, за да стартирате проекта.

Стъпка 4: Изграждане на PWM модул- Дизайн на блок и настройка на файл за ограничения (I)

В Flow Navigator кликнете върху „„ Създаване на дизайн на блок “, след което натиснете OK. щракнете върху знака „+“, за да добавите необходимите IP адреси. Добавете:

- Една обработваща система ZYNQ7 Два AXI таймера

- Два AXI таймера

Стъпка 5: Изграждане на PWM модул- Дизайн на блок и настройка на файл за ограничения (II)

След добавяне на IP адреси, стартирайте Block Automation и автоматизация на връзката. След като автоматизацията приключи, в блока „axi_timer_0“щракнете с десния бутон върху pwm0 -> Make External. Назовете външния щифт pwm0 като pwm_Xaxis. Също така, повторете горния процес на блока „axi_timer_1“и наречете външния щифт pwm0 като pwm_Zaxis.

Стъпка 6: Изграждане на ШИМ модул- Дизайн на блок и настройка на файл за ограничения (III)

Забележете, че всеки път, когато завършим Block Design във Vivado, трябва да създадем HDL Wrapper. Тъй като това ще бъде модул от най-високо ниво за всеки проект.

Стъпка 7: Изграждане на PWM модул- Дизайн на блок и настройка на файл за ограничения (IV)

Сега трябва да настроим нашия ограничителен файл, за да присвоим щифтове, свързани към нашата блокова диаграма. Затворете прозореца за проектиране на блокове, в раздела Източници, „Добавяне на източници“-> Добавяне или създаване на ограничения-> добавяне на Zybo-Master.xdc като наши файлове с ограничения.

Стъпка 8: Изграждане на PWM модул- Дизайн на блок и настройка на файл за ограничения (V)

Отворете ограничителния файл Zybo-Master.xdc от папката Constraints, декомментирайте портовете, които искаме да посочим като изходни сигнали, и преименувайте „get_ports {XXXX}“, което XXXX обозначава външния щифт, посочен в блоковата диаграма. Настройката на ограничителния файл е показана на фигурата.

Стъпка 9: Изграждане на PWM модул- инсталиране на хардуер

Свържете серводвигателите към Pmod CON3. TowerPro SG90 е моделът на серво мотор, който използвахме в този проект. За проводниците на серво мотора оранжевият проводник представлява ШИМ сигнала, свързан към щифт SIG в Pmod CON3. Червеният проводник Vcc е захранващ проводник, свързан към VS щифт в Pmod CON3. И накрая, кафявият проводник Gnd е заземен проводник, свързан към щифта GND. След това поставете Pmod CON3 в горния ред на JD порта в Zybo Board.

Стъпка 10: Изграждане на PWM модул- Генериране на битстрийм и стартиране на SDK

1. В раздела Project Navigator стартирайте Generate BitStream.

2. Експортирайте хардуер: Файл> Експорт> Експортиране на хардуер-> маркирайте върху „включване на битов поток“-> OK 3. Стартирайте SDK: Файл-> Стартиране на SDK.

Стъпка 11: Изграждане на PWM модул- Създайте ново приложение в Xilinx SDK

Създайте ново приложение:

File> New> Application Project -> Въведете името на вашия проект -> Finish

Под Project Explorer трябва да има три папки.

В този случай „design_1_wrapper_hw_platform_0“е папката, експортирана по -рано от Vivado. Axis_2_PWM_SDK_bsp е папката за поддръжка на борда. А Axis_2_PWM_SDK е нашата основна папка за проекти в SDK. Можете да видите файла „helloworld.c“в папката „src“на Axis_2_PWM_SDK, където „helloworld.c“е основният файл.

Стъпка 12: Изграждане на PWM модул- преглед на Project Explorer (I)

Нека проверим някои файлове в Project Explorer. Първо, в папката „design_1_wrapper_hw_platform_0“отворете „system.hdf“. Този файл демонстрира картата на адресите на процесора ps7_cortex9 и IP блоковете, присъстващи в нашия дизайн.

Стъпка 13: Изграждане на PWM модул- преглед на Project Explorer (II)

След това проверете файловете „include“и „libsrc“в папката „Axis_2_PWM_SDK_bsp“. Библиотечните файлове тук ни позволяват да взаимодействаме с хардуерни периферни устройства, без да „играем“регистри.

Стъпка 14: Изграждане на PWM модул- Преглед на Project Explorer (III)

Чрез документацията за BSP xtmrctr.h се намира като Xilinx Timer Control Library, свързана с AXI Timer. Обикновено тук бихме могли да намерим желаната PWM функция. Ако обаче прочетете документацията „tmrctr_v4_3“, това показва, че драйверът в момента не поддържа PWM операцията на устройството. Поради дефицита в PWM функцията, трябва да завършим нашата PWM функция с помощта на xtmrctr.h и AXI Timer v2.0 LogiCORE IP Product Guide.

Стъпка 15: Изграждане на PWM модул- приключване на PWM функция (I)

Обратно към основния файл „helloworld.c“, включвайте следните заглавни файлове:

Стъпка 16: Изграждане на PWM модул- приключване на PWM функция (II)

Определете базовите адреси на два AXI TImer чрез „xparameters.h“.

Стъпка 17: Изграждане на PWM модул- приключване на PWM функция (III)

Изградете желаната PWM функция.

Duty_val: преобразува стойността на степента в работен цикъл. PWM_Freq_Duty: задава желаната честота и работен цикъл за генериране на PWM. Трябва да се определи и часовник.

PWM_START: задайте адреса на PWM регистъра и започнете да генерирате PWM.

PWM_STOP: задайте адреса на PWM регистъра и спрете генерирането на PWM.

Останалата част от демо кода е показана в „helloworld.c“под „Axis_2_PWM_SDK“

Стъпка 18: Изграждане на PWM модул- Накарайте го да работи

1. Програмирайте FPGA чрез SDK

- Свържете Zybo Board чрез USB порт към компютър.

- Инструменти на Xilinx -> Програма FPGA

2. Стартирайте програмата

Кликнете върху иконата „Изпълнение“и от падащото меню -> Изпълнение като -> Стартиране на хардуер

3. Терминал SDK

- Отворете терминала на SDK -> Свързване към сериен порт -> OK

- Стартирайте програмата. Ако демонстрационният код работи успешно, трябва да видите „Инициализацията е извършена!“на терминала SDK.

Стъпка 19: Обработка на поточно видео на Digilent ZYBO с OV7670

Приложен е пълен архивен файл.

Стъпка 20: Пълна блокова диаграма

Това показва пълната диаграма на всички връзки и IP блокове в проекта

Стъпка 21: Свържете OV7670 към ZYBO

Създайте връзка, за да свържете модула ov7670 към ZYBO Pmods

Данните Pmod са Pmod D

Контрол Pmod е Pmod C

Освен това, свържете PmodCON3 и сервомоторите, както е посочено в първата половина на този урок

Стъпка 22: Създайте дизайн на блок

В Flow Navigator кликнете върху „Създаване на дизайн на блок“, след което натиснете OK.

Стъпка 23: Добавете VHDL файлове за управление и заснемане на камера OV7670

Добавете VHDL файловете, приложени към тази стъпка, към проекта

Стъпка 24: Добавете файл с ограничения

Добавете прикачения файл с ограничения към вашия проект.

Стъпка 25: Добавете IP Repo за HLS IP

Вземете прикачения Zip файл и го разархивирайте в нова папка, наречена по подобен начин в нова директория (папка), наречена "HLS_repo".

Добавете IP хранилище към вашия проект, като отидете в IP каталога и щракнете с десния бутон, като изберете „Добавяне на хранилище …“

Придвижете се до вашата директория "HLS_repo" и я изберете.

По избор: Създайте за себе си блока за обработка на видео HLS!

Стъпка 26: Добавете модули и IP

Добавете модулите ov7670_axi_stream_capture, debounce и ov7670_controller към блоковата диаграма, като щракнете с десния бутон върху фона и изберете "Добавяне на модул …"

По същия начин добавете IP адресите:

- HLS_Video_Track

- Запис на буфер на видео рамка

- Прочетете буфера за видеокадри

- Контролер за видео синхронизация

- AXI4-поток към видео изход

- 3 от "Парче"

- Постоянен

- 2 на AXI таймер

Стъпка 27: Настройки за IP конфигурация

Както е показано на снимките

Стъпка 28: Добавете и конфигурирайте PS IP блок

Добавете системата за обработка ZYNQ7 към блоковата диаграма

редактирайте конфигурацията:

-

PS-PL конфигурация

-

HP

- Активирайте S HP 0

- Активирайте S HP 1

-

-

Конфигурация на часовника

-

PL Часовници от плат

- FCLK_0 при 100MHz

- FCLK_1 при 25MHz (OutputClock)

- FLCK_2 при 35MHz (<= 50MHz) (CameraClock)

-

Стъпка 29: Част 1. Изграждане на ШИМ модул за серво мотори

Изведете axi_timer_0 pwm0 към новия изходен порт pwm_Xaxis

Изведете axi_timer_1 pwm0 към новия изходен порт pwm_Zaxis

Стъпка 30: Видеовходни странични връзки (aclk подчертано)

Свържете правилно IP блоковете на страната на видео входа

(* тези връзки трябва да бъдат създадени чрез избор на правилните опции по време на автоматизация на връзката) "aclk" от axi_stream_capture отива на:

- ap_clk при запис на буфер на видео кадър

- ap_clk на блока за обработка на видеопоток HLS

- *aclk на AXI smartconnect IP от буфера за видеокадър Запишете в S_AXI_HP0

- *aclk, съответстващ на каналите на AXI Interconnect IP за каналите S_AXI на блока за обработка на видео HLS и буфера за видеокадър, запишете S_AXI_HP0_ACLK на блока PS

Сигналът на видео потока е просто свързан последователно от блока за улавяне към интерфейса на паметта Zynq.

- Видеото преминава от блок за улавяне към блок за обработка на HLS.

- Обработеното видео от блока HLS отива в блока за запис на буфера на кадрите.

- *Блокът за запис на буфер на рамка се свързва с интерфейса HP0 на блока Zynq PS.

- Сигналът m_axis_tuser от изхода на блока за улавяне се свързва ръчно към входния сигнал video_in_TUSER на блока за обработка на HLS и към сигнала ap_start на същия блок.

Сигналът TUSER (tuser) се използва от протокола за видеопоток AXI, за да покаже началото на кадър от видеото. AP_Start казва на блока HLS да започне обработка. По този начин използваме tuser за задействане на блока HLS за обработка на всеки кадър при влизане. Когато свързвате един сигнал на шина и го разделяте по този начин, е необходимо също да го свържете към нормалната точка на завършване на останалата част от шината. Vivado приема, че ако свързвате сигнала ръчно, искате да прекъснете връзката, към която обикновено се свързва.

Конфигурационни настройки на IP блокове:

Запис на буфер на видео кадър:

Видео формати: RGB8

1 извадка на часовник Макс колони: 1280 (> = 640) Макс редове: 960 (> = 480) Максимална ширина на данните: 8

Стъпка 31: Връзки с OV7670

На блока ov7670_axi_stream_capture

- Направете всички входове външни (щракнете с десния бутон върху щифт и изберете от менюто, или кликнете с левия бутон-> ctrl+T)

- Оставете имената такива, каквито са

На блока ov7670_controller

- Направете всички блокови изходи външни

- Преименувайте порта config_finished на led0

- свържете clk към CameraClock (<= 50MHz) (FCLK_2)

На деблокиращия блок

- свържете входа button1 към външен входен порт, наречен btn0

- свържете out1 към линията за повторно изпращане на IP блока ov7670_controller

- свържете входа button2 към външен входен порт, наречен btn3

- свържете out2n към входа ext_reset_in на IP за нулиране на системата на процесора за домейна на часовника за заснемане на видео. (*Това може да се наложи да се направи след генерирането на този IP*)

- свържете clk към CameraClock (<= 50MHz) (FCLK_2)

Стъпка 32: Връзки от външната страна на видеото

Връзки за блокове Video Timing Controller (VTC), AXI4-Stream към Video Out и филийки

- Използвайте 25MHz часовник (FCLK_1) за vid_io_out_clk и VTC clk

- Използвайте 100MHz часовник (FCLK_0) за връзка с AXI4-Stream към видео изход

- vtiming_out към vtiming_in

- Video Frame Buffer Read m_axis_video отива в AXI4-Stream към Video Out video_in

- vtg_ce отива на gen_clken

- Свържете VTC clken, aclken, vid_io_out_ce с Constant dout [0: 0]

- Изведете vid_hsync и vid_vsync към външни изходни портове vga_hs и vga_vs съответно. (не е на снимката)

Филийки:

-

Филийките трябва да бъдат настроени, както е показано на приложените снимки

- преименувайте блоковете на slice_red, slice_green и slice_blue

- настройка на диапазони на срезове, както е показано на изображенията към името на блока

- свържете всеки изходен отрязък към изход на външен порт, както е показано на изображението.

- vid_data [23: 0] се свързва с входовете за всеки фрагмент (Din [23: 0])

Стъпка 33: Изпълнете автоматизация на блокиране и свързване

Изпълнете Block Automation, за да свържете нещата от блока ZYNQ7 PS. Както е показано на снимката.

Изпълнете автоматизация на връзката, за да създадете всички IP за взаимосвързаност. Обърнете специално внимание на всички опции във всяка снимка.

В блока за деблокиране свържете out2n към домейна на часовника за заснемане на видео Процесорна система за нулиране на процесора ext_reset_in вход.

Стъпка 34: Генерирайте HDL Wrapper

Генерирайте HDL Wrapper за вашия блок дизайн.

Задайте го като най -горния модул.

Стъпка 35: Генерирайте Bitstream, експортирайте хардуера в SDK, стартирайте SDK от Vivado

Не забравяйте да включите битовия поток в експорта.

Генерирането на битов поток може да отнеме много време.

След това стартирайте SDK

Стъпка 36: SDK (без FreeRTOS)

Тази версия прави всичко, без да използва FreeRTOS, като кондензира добре кода.

Създайте самостоятелен BSP въз основа на хардуерния дизайн. Опциите по подразбиране трябва да са наред. Уверете се, че са генерирани източници на BSP.

Създайте приложение, както е показано на картинката. (празно приложение)

Изтрийте автоматично генерирания основен файл и импортирайте прикачените файлове.

Стъпка 37: Изпълнение на FreeRTOS

Тази версия използва FreeRTOS. Създайте FreeRTOS901 BSP въз основа на хардуерния дизайн. Опциите по подразбиране трябва да са наред. Уверете се, че са генерирани източници на BSP.

Създайте приложение, както е показано на картинката. (празно приложение)

Изтрийте автоматично генерирания основен файл и импортирайте прикачените файлове.

Стъпка 38: Инструкции за употреба

Този проект е малко труден за изпълнение. Следвайте стъпките по ред.

Уверете се, че вашият ZYBO не се зарежда самостоятелно, когато се включи. Това означава, че светодиодът „Готово“не трябва да свети. Един от начините да направите това е да настроите джъмпера за източник на зареждане на JTAG.

Отворете проекта (FreeRTOS или не), който искате да програмирате от SDK

- Включете вашия ZYBO. Светодиодът Done (Готово) не трябва да свети.

- Програмирайте FPGA с битов файл. Индикаторът „Готово“трябва да светне. Led0 не трябва да свети.

- Изпълнете кода (не забравяйте да преминете през началната точка на прекъсване, ако правите това).

В този момент трябва да получите изход на вашия VGA дисплей.

За да рестартирате (ако има грешки или каквото и да е): бързо докоснете бутона PS-SRST или изключете ZYBO и след това отново включете. Продължете от стъпка 2.

Спирането на процесора с инструмента за отстраняване на грешки ще накара камерата да задържи позиция, вместо да се движи. Видео потокът така или иначе ще продължи.

Стъпка 39: Препратки и връзки

Референтни ръководства и документация за Xilinx:

- PG044 - AXI -Stream към видео изход

- PG278 - Буфер за четене/запис на видеокадър

Други връзки:

- Блогът на Лаури - вход за VDMA

- Блогът на Лаури - OV7670 към VGA изход с помощта на BRAM

- Hamsterworks wiki, от Mike Fields, първоизточник на кода OV7670

- Информационен лист, показващ основните спецификации на времето

Препоръчано:

Лесна промяна на цвета, базирана на наклона, безжична лампа с куб Рубик: 10 стъпки (със снимки)

Лесна промяна на цвета, базирана на наклона, безжична лампа с кубик на Рубик: Днес ще изградим тази страхотна лампа с кубик на Рубик, която променя цвета в зависимост от това коя страна е нагоре. Кубът работи на малка LiPo батерия, заредена от стандартен micro-usb кабел и, според моите тестове, има живот на батерията от няколко дни. Това

RC автомобил с Bluetooth контрол с контрол на скоростта и измерване на разстоянието: 8 стъпки

RC автомобил с Bluetooth контрол с контрол на скоростта и измерване на разстоянието: Като дете винаги съм бил очарован от RC колите. В днешно време можете да намерите много уроци, за да направите сами евтини RC автомобили с Bluetooth, с помощта на Arduino. Нека направим още една крачка напред и използваме нашите практически познания по кинематика, за да изчислим

Контрол на щорите с ESP8266, Google Home и Openhab интеграция и уеб контрол: 5 стъпки (със снимки)

Контрол на щори с ESP8266, интегриране и уебконтрол на Google Home и Openhab: В тази инструкция ще ви покажа как добавих автоматизация към моите щори. Исках да мога да добавя и премахвам автоматизацията, така че цялата инсталация е закрепена. Основните части са: Стъпков двигател Стъпков шофьор, управляван от bij ESP-01 Gear и монтаж

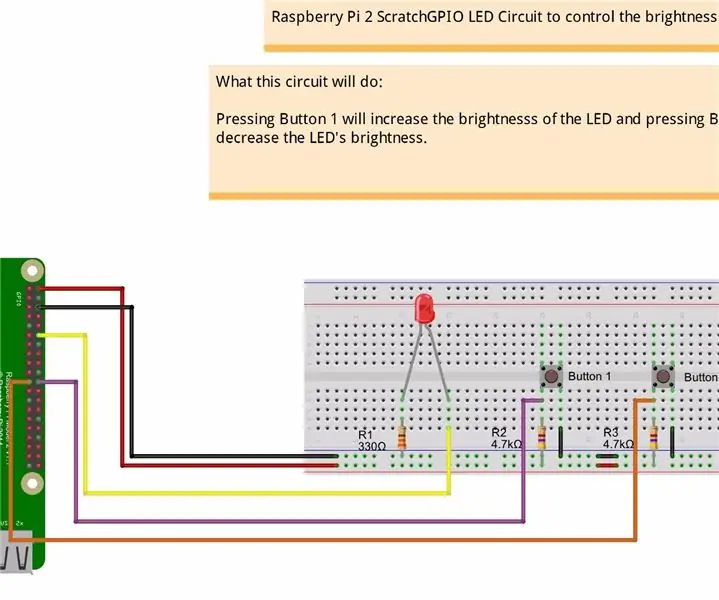

Контрол на яркостта ШИМ базиран LED контрол с помощта на бутони, Raspberry Pi и надраскване: 8 стъпки (със снимки)

Контрол на яркостта PWM управление на LED управление с помощта на бутони, Raspberry Pi и Scratch: Опитвах се да намеря начин да обясня как PWM работи на моите ученици, затова си поставих задачата да се опитам да контролирам яркостта на светодиода с помощта на 2 бутона - единият бутон увеличава яркостта на светодиода, а другият го затъмнява. Към програмата

Уеб камера в камера със соколино око: 3 стъпки (със снимки)

Уеб камера в камера с ястребино око но не намерих идеалния случай за това. Харесвам