Съдържание:

- Стъпка 1: Добавете източници и изберете „Добавяне или създаване на източници на симулация

- Стъпка 2: Създайте файл, наречен Enable_sr_tb

- Стъпка 3: Създайте файл Testbench

- Стъпка 4: Задайте Enable_sr_tb като най -високо ниво под симулацията

- Стъпка 5: Изпълнете синтез и поведенческа симулация

- Стъпка 6: Оценете резултата от симулацията

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 07:53.

- Последно модифициран 2025-01-23 14:36.

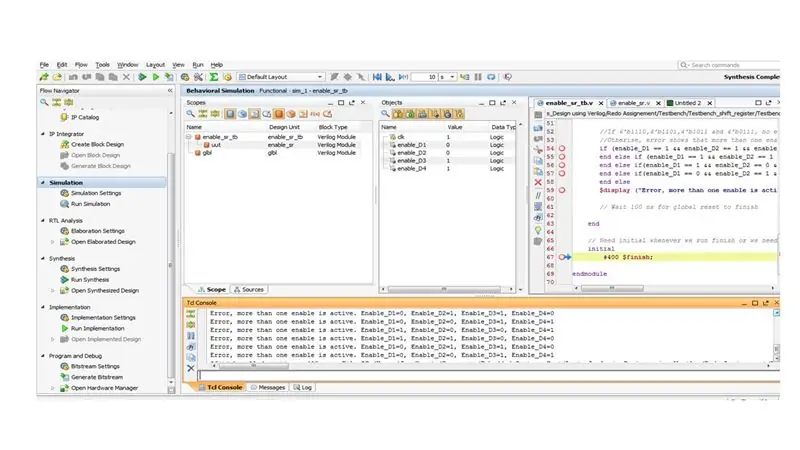

Направих този симулационен проект за онлайн клас. Проектът е написан от Verilog. Ще използваме симулация във Vivado, за да визуализираме формата на вълната в enable_sr (цифра за активиране) от предварително създадения проект за хронометър. Освен това ще използваме системната задача за показване на грешки, направени от нас при проектирането.

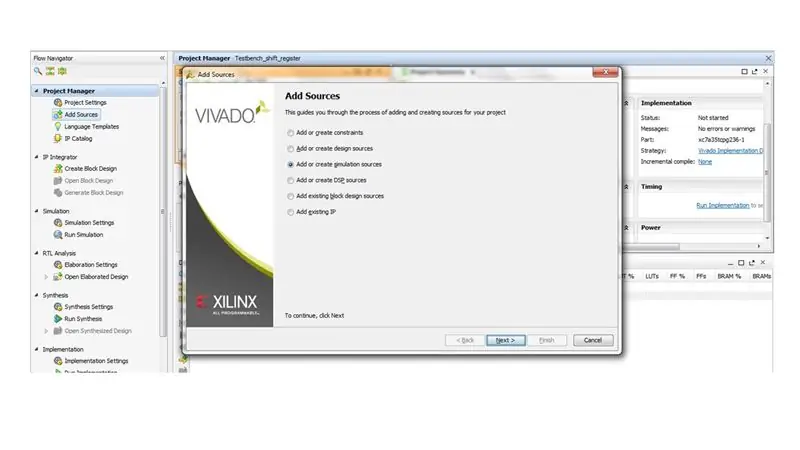

Стъпка 1: Добавете източници и изберете „Добавяне или създаване на източници на симулация

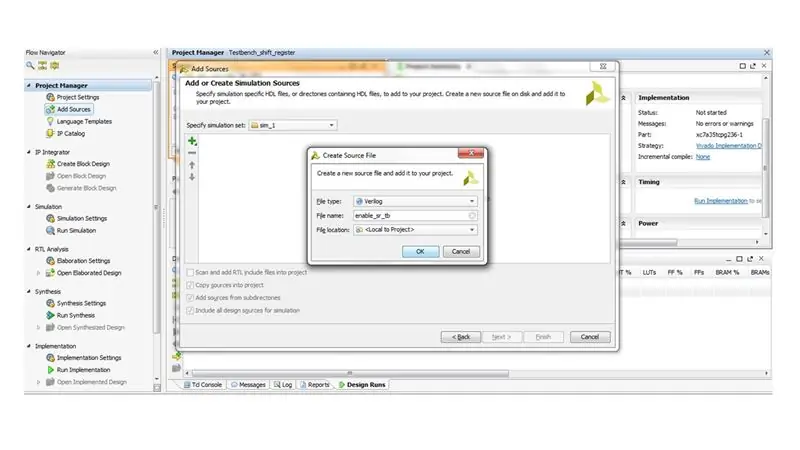

Стъпка 2: Създайте файл, наречен Enable_sr_tb

Стъпка 3: Създайте файл Testbench

1. Импортирайте модула enable_sr от проекта за хронометър. Това е файлът, който искаме да симулираме

2. Създайте модул testbench enable_sr_tb ();

3. Въведете входове и изходи на модула enable_sr (). Не забравяйте, че входовете за enable_sr вече са в регистър, докато изходите стават мрежови.

4. Инстанцирайте тестваната единица (uut), която е enable_sr

5. Генерирайте часовник, който период (T) е 20ns

6. Използвайте условния израз, за да създадете система за проверка на грешки. В този пример искаме да проверим дали има повече от една цифра.

Забележка: В оригиналния файл enable_sr () трябва да инициализираме шаблона като 4’b0011, така че да са активни две цифри за създаване на грешка

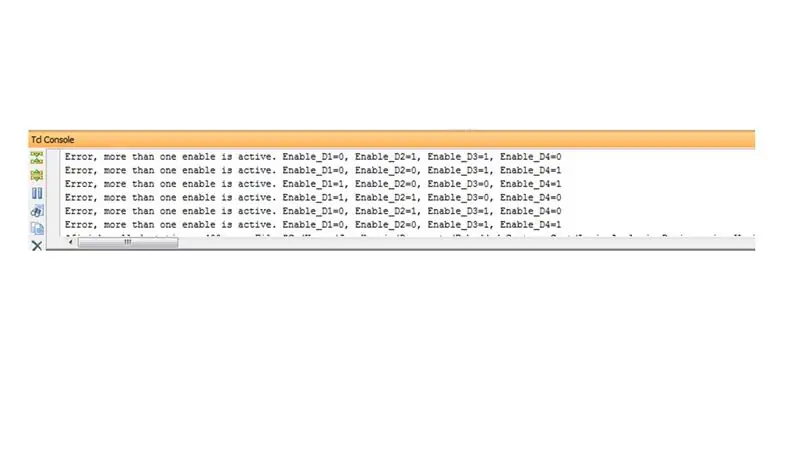

7. Използвайте системната задача $ display, за да покажете грешката

8. Използвайте системна задача $ finish, за да завършите симулацията при момент 400ns

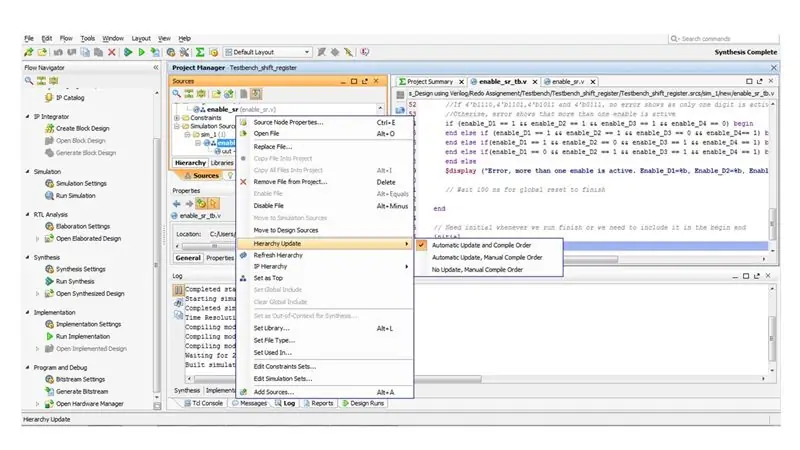

Стъпка 4: Задайте Enable_sr_tb като най -високо ниво под симулацията

Стъпка 5: Изпълнете синтез и поведенческа симулация

- Преди да стартирате поведенческа симулация, стартирайте синтеза, за да се уверите, че няма синтаксични грешки във файла testbench и единицата в тестовия файл

- Изпълнете поведенческата симулация

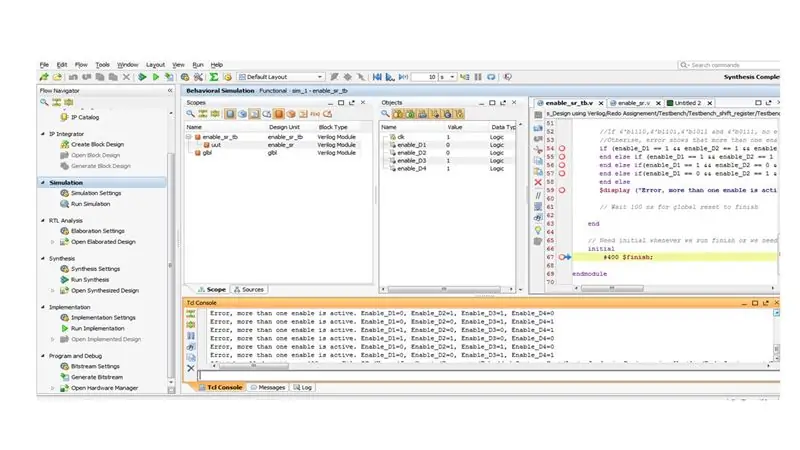

Стъпка 6: Оценете резултата от симулацията

Ще видите прозорците за симулация. Съдържа различни панели.

Ще видите съобщението за грешка в панела на конзолата. Това показва, че по време на симулацията са активни повече от една цифра.

Можете също да видите формата на вълната в обхвата

Приложен е проектният файл.

Препоръчано:

Как да постигнете съпротивление/капацитет, като използвате компоненти, които вече имате !: 6 стъпки

Как да постигнете всякакво съпротивление/капацитет с помощта на компоненти, които вече имате !: Това не е просто поредният калкулатор на серия/паралелно еквивалентно съпротивление! Тази програма изчислява как да комбинирате резистори/кондензатори, които в момента имате, за да постигнете целевата стойност на съпротивлението/капацитета, от която се нуждаете. Имали ли сте някога спецификация

Visuino Как да използвате модулация на импулсната ширина (PWM) за промяна на яркостта на светодиода: 7 стъпки

Visuino Как да използваме Pulm Width Modulation (PWM) за промяна на яркостта на LED: В този урок ще използваме LED, свързан към Arduino UNO и Visuino, за да променим яркостта му с помощта на Pulme Width Modulation (PWM). Гледайте демонстрационен видеоклип

Как да създадете Linux зареждащо устройство (и как да го използвате): 10 стъпки

Как да създадете зареждащо устройство на Linux (и как да го използвате): Това е просто въведение за това как да започнете с Linux, по -специално Ubuntu

Как да използвате стъпков двигател като въртящ се енкодер и OLED дисплей за стъпки: 6 стъпки

Как да използвате стъпков двигател като въртящ се енкодер и OLED дисплей за стъпки: В този урок ще се научим как да проследяваме стъпките на стъпковия двигател на OLED дисплея. Гледайте демонстрационен видеоклип. Кредитът за оригиналния урок отива на потребителя на youtube " sky4fly "

Как да използвате Mac терминал и как да използвате ключови функции: 4 стъпки

Как да използвате Mac терминал и как да използвате ключови функции: Ще ви покажем как да отворите MAC терминала. Също така ще ви покажем няколко функции в терминала, като ifconfig, промяна на директории, достъп до файлове и arp. Ifconfig ще ви позволи да проверите вашия IP адрес и вашата MAC реклама