Съдържание:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 07:51.

- Последно модифициран 2025-01-23 14:36.

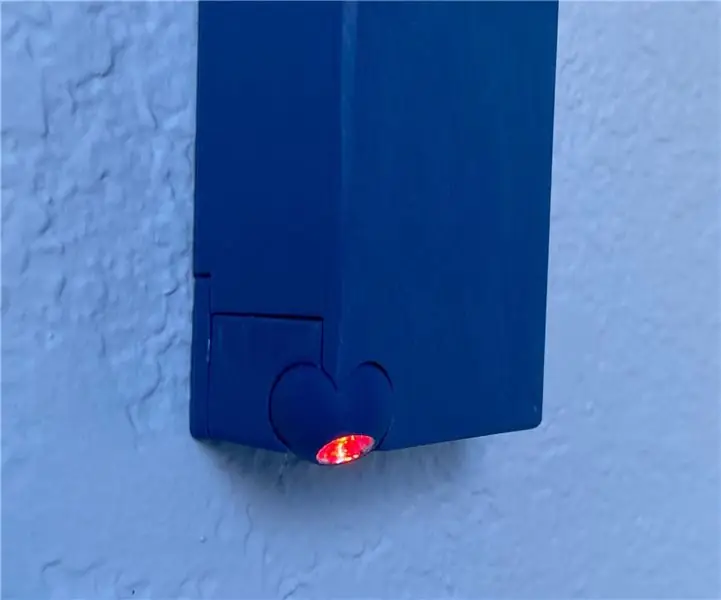

Нашата цел с този проект беше да създадем нещо, което да спести енергия и финансови ресурси на общностите. Уличните светлини с активирано движение биха направили и двете неща. В цялата страна енергията се губи в улично осветление, осветяващо празни улици. Нашата система за улично осветление гарантира, че светлините са включени само когато е необходимо, спестявайки на общностите безброй долари. С помощта на датчици за движение системата включва светлини само когато има автомобили. Също така за безопасността на пешеходците, ние внедрихме бутон за отмяна, който включва всички светлини на улицата. Следващите стъпки ще ви разкажат как сме проектирали и изградили нашия намален модел на проекта, използвайки Vivado и дъска Basys 3.

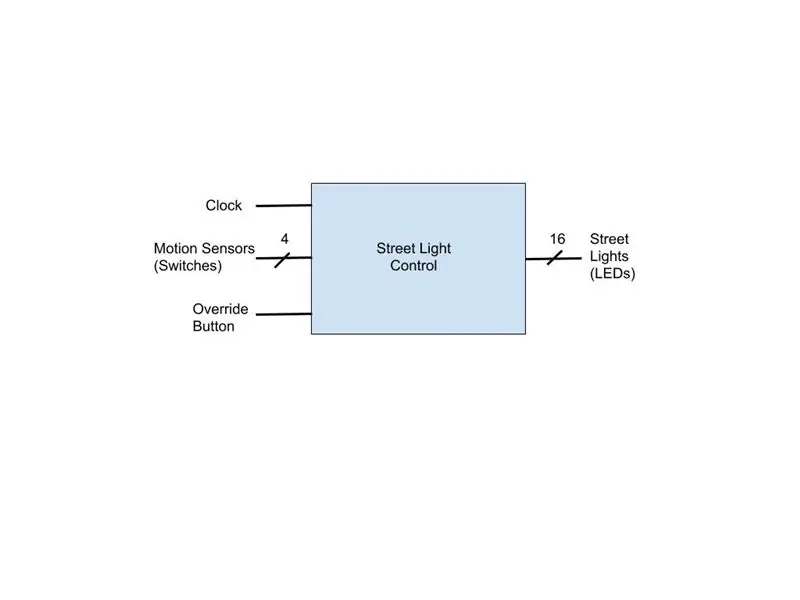

Стъпка 1: Системна черна кутия

Започнахме този проект, като начертахме проста диаграма с черна кутия. Диаграма в черна кутия просто показва входовете и изходите, които нашата система изисква, за да завърши всички необходими процеси. Опитахме се да запазим нашия дизайн възможно най -прост и основен. Трите ни системни входа включват шина от сензори за движение (4 за нашия намален модел), бутон за управление на пешеходци и вход за часовник. От другата страна единственият ни изход е шина от LED светлини, представляващи нашите улични светлини. За този модел използвахме сценарий от 16 улични светлини, просто защото това е максималният брой вградени LED изходи на платката Basys 3. И накрая, използвайки тази диаграма, успяхме да създадем нашия проект, източник и ограничения на Vivado с подходящи входове и изходи.

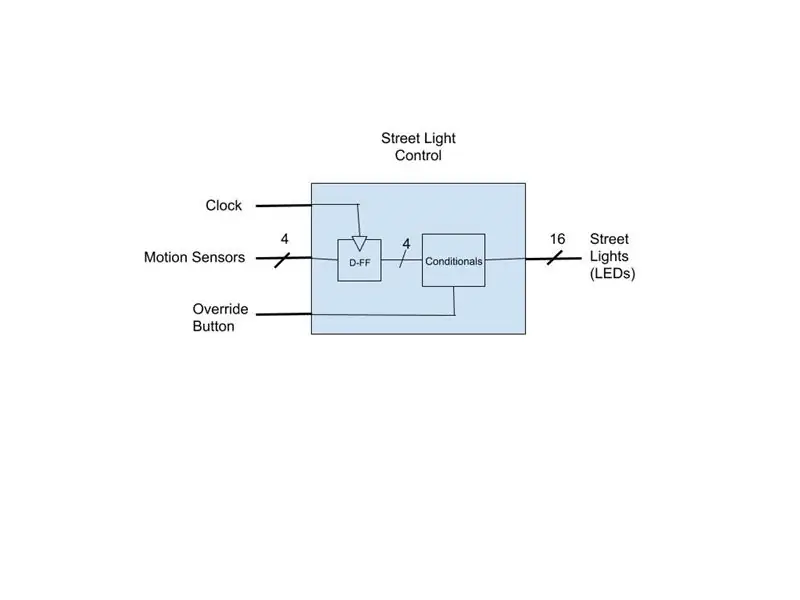

Стъпка 2: Компоненти

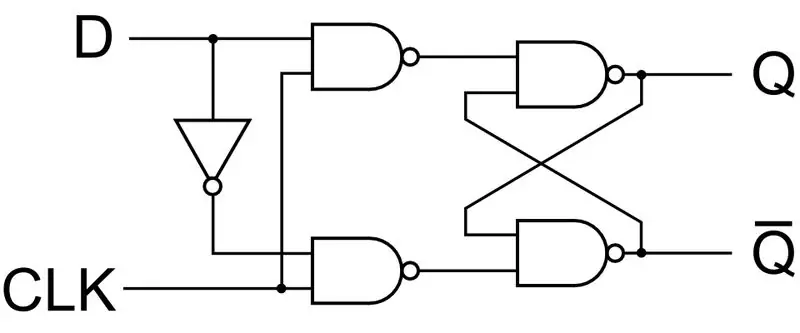

В тази стъпка се задълбочаваме, разглеждайки компонентите, съставляващи нашата диаграма на черната кутия. Първият ни компонент е VHDL изходен файл, съдържащ D джапанки. D джапанките просто приемат сигнала, който се подава към тях от сензорите на нарастващия ръб на часовника, и захваща тези данни до следващия нарастващ фронт. Това предпазва нашите чувствителни сензори за движение да не предизвикват "трептене" на изходните светодиоди. Също така, ние поставяме един D джапанка на входния сигнал на бутона, за да запазим светодиодите за около 5-7 секунди след натискането на бутона. Също така проведохме това през разделител на часовник.

обект clk_div2 е Port (clk: в std_logic; sclk: out std_logic); край clk_div2;

архитектурата my_clk_div на clk_div2 е

постоянен макс_ брой: цяло число: = (300000000); сигнал tmp_clk: std_logic: = '0'; започнете my_div: process (clk, tmp_clk) променлива div_cnt: integer: = 0; започнете, ако (нарастващ ръб (clk)), след това ако (div_cnt = MAX_COUNT), тогава tmp_clk <= не tmp_clk; div_cnt: = 0; else div_cnt: = div_cnt + 1; край ако; край ако; sclk <= tmp_clk; край на процеса my_div; край my_clk_div;

Нашият последен компонент в тази диаграма е поведенчески VHDL изходен файл, съдържащ условни условия за изходите, базирани на конфигурацията на входните сигнали.

Стъпка 3: D Джапанки

Четирите джапанки, прикрепени към входните сигнали, са от съществено значение за функционалността на нашата система. Както бе споменато по-рано, с чувствителни сензори за движение и бутон за отмяна, джапанките използват ключалки, за да извеждат само входния ни сигнал върху нарастващия ръб на часовника. Тази последователна логика означава, че нашите улични светлини могат да останат включени за определен период от време, след като се задействат от бързо движение. Кодирането на D-Flip Flop е доста просто:

beginprocess (CLK) start if rise_edge (CLK) then Q <= D; край ако; краен процес;

Цялото нещо може да се компилира в едно изявление if. След като получихме това парче, създадохме структурен VHDL изходен файл, съдържащ всичките четири от нашите необходими джапанки:

започнете DFF0: Карта на порт DFF (CLK => CLK, D => D (0), Q => Q (0)); DFF1: DFF порт карта (CLK => CLK, D => D (1), Q => Q (1)); DFF2: Карта на DFF порт (CLK => CLK, D => D (2), Q => Q (2)); DFF3: Карта на DFF порт (CLK => CLK, D => D (3), Q => Q (3));

край Поведенчески;

Това помага да запазим нашия главен структурен файл, където събираме всички компоненти на системата много по -чисти и организирани.

Стъпка 4: Условия

За да запазим кода си компактен и ефективен, ние написахме всичките си условни условия в един -единствен случай. За нашия намален модел имахме 16 възможни LED изходни конфигурации, тъй като всеки датчик за движение отговаря за група от 4 светодиода.:

случай NMS е когато "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; краен случай;

Стъпка 5: Ограничения

За да посочите правилно вашите входове и изходи с помощта на Vivado, трябва да внедрите файл с ограничения, който посочва всички използвани портове, бутони, светодиоди и часовници.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [1]} PACK U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property PACKAGE_PIN W18 get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE_PIN U14 [get LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 [get_ports {LED 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] IO set_property STANDARD LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11]}] set_property IOS33 [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOSTANDARD LVCMOS33 {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCMOS33 [get_ports [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [1PP] PAGE B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

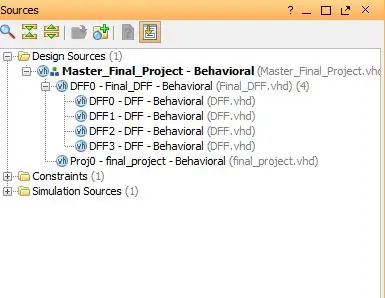

Стъпка 6: Основен изходен файл

В този основен файл ние събираме всички източници на компоненти, споменати по -горе. Този файл функционира като структурен код, обединяващ различни компоненти.

обект Master_Final_Project е порт (BTN: в STD_LOGIC; CLK: в STD_LOGIC; MS: в STD_LOGIC_VECTOR (3 надолу 0); LED: изход STD_LOGIC_VECTOR (15 надолу 0)); край Master_Final_Project;

архитектура Поведението на Master_Final_Project е

компонент final_project е Port (--CLK: в STD_LOGIC; NMS: в STD_LOGIC_VECTOR (3 downto 0); BTN: in STD_LOGIC; --sw: in STD_LOGIC_Vector (1 downto 0); LED: out STD_LOGIC_VECTOR (15 downto 0); краен компонент;

компонент Final_DFF е

Порт (CLK: в STD_LOGIC; D: в STD_LOGIC_Vector (3 надолу 0); Q: изход STD_LOGIC_Vector (3 надолу 0)); краен компонент;

сигнал DFF02proj30: STD_LOGIC;

сигнал DFF12proj74: STD_LOGIC; сигнал DFF22proj118: STD_LOGIC; сигнал DFF32proj1512: STD_LOGIC;

започнете

DFF0: Карта на крайния_DFF порт (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: карта на порт на final_project (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); край Поведенчески;

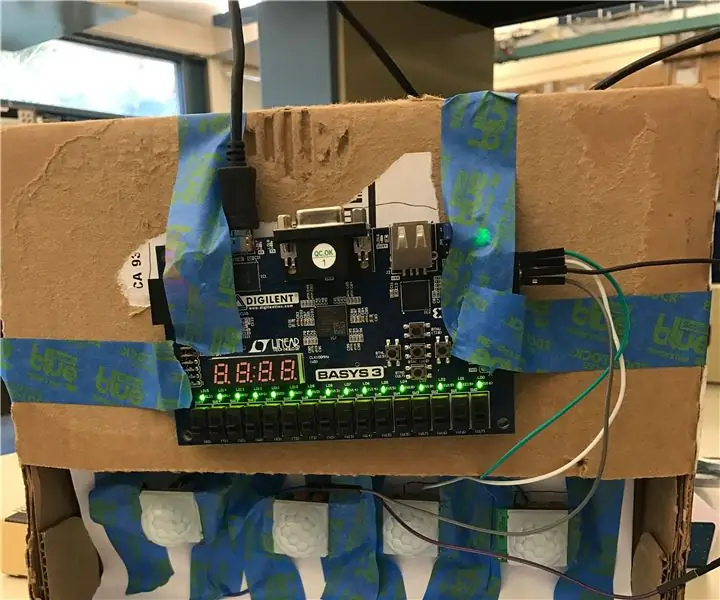

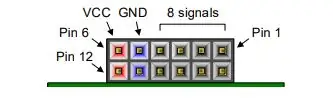

Стъпка 7: Монтаж

Хардуерният монтаж за този проект е минимален. Единствените необходими парчета са както следва:

1. Базис 3 дъска (1)

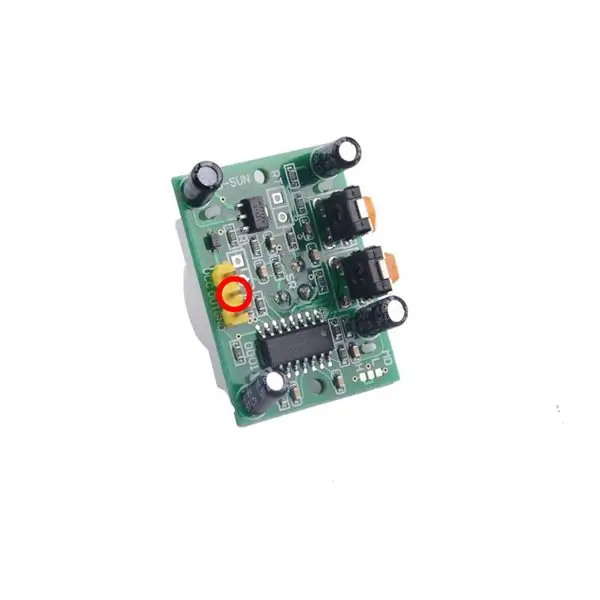

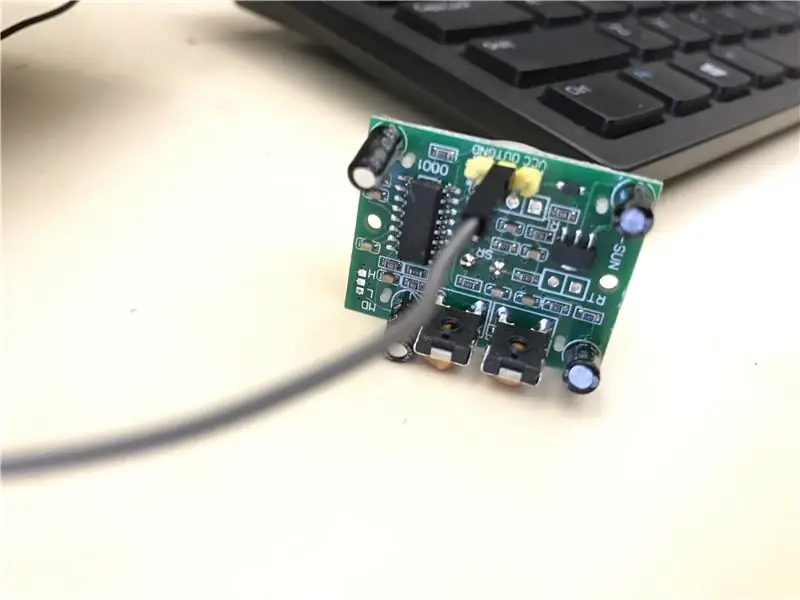

2. Евтини сензори за движение, които можете да намерите на Amazon тук. (4)

3. Отвод за мъже към жени (4)

Монтаж:

1. Свържете 4 мъжки проводника към JB портове 1-4 на заглавието на PMod (вижте фигурата).

2. Свържете женските краища към изходния щифт на всеки сензор за движение.

Стъпка 8: Зареждане на програмата

Сега сме готови да заредим VHDL главния изходен файл на платката Basys 3. Уверете се, че сте стартирали синтез, внедряване и генерирате проверка на битов поток за евентуални грешки. Ако всички се изпълняват успешно, отворете хардуерния мениджър и програмирайте устройството Basys 3. Вашият проект вече е завършен!

Препоръчано:

Крила за косплей с активирано движение, използващи Circuit Playground Express - Част 1: 7 стъпки (със снимки)

Крила за косплей с активирано движение, използващи Circuit Playground Express - Част 1: Това е първа част от проект от две части, в който ще ви покажа моя процес на създаване на чифт автоматизирани феерични крила. Първата част от проекта е механиката на крилата, а втората част я прави носеща и добавя крилата

Автоматични улични светлини с помощта на ултразвуков сензор: 3 стъпки

Автоматични улични светлини с помощта на ултразвуков сензор: Мислили ли сте някога, че уличните светлини автоматично се включват през нощта и се изключват автоматично сутрин? Има ли някой, който да включи/изключи тези светлини? Има няколко начина за включване на уличното осветление, но следното c

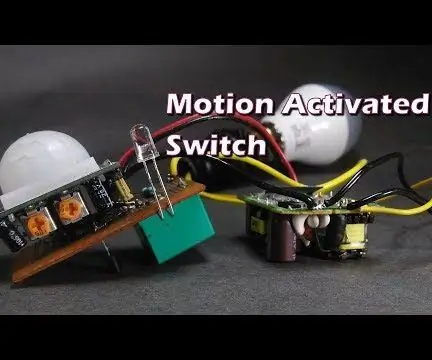

Превключвател на лампа с активирано движение: 3 стъпки

Превключвател на лампа с активирано движение: Когато напускаме бюрото или стаята си, през повечето време забравяме да изключим осветлението там. Това води до загуба на електроенергия и увеличаване на сметката ви за електроенергия. Но какво, ако светлините се изключат автоматично, след като излезете от стаята. Да в

Стълби с активирано движение: 6 стъпки (със снимки)

Стълби с активирано движение: Да, знам какво си мислите, това изглежда малко пресилено, но първо, никога няма да се притеснявате, че ще убодете пръста си отново и второ, това кара ходенето нагоре и надолу по стълбите ви толкова много забавно, аз се качих горе без причина

Как да си направим озвучителна система за колички за улични партита: 10 стъпки

Как да си направим звукова система за колички за пазаруване на улични партита: Тази инструкция ще ви покаже стъпките за създаване на самостоятелна мобилна звукова система в количка за пазаруване. Тази настройка може да се използва за всякакви публични събирания, включително протести, партита на уличните танци, паркинг парчета, много рап битки и дори изпреварване