Съдържание:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 07:51.

- Последно модифициран 2025-01-23 12:58.

Свържете вашата платка за развитие Mojo към външни входове с този щит.

Какво представлява бордът за развитие на Mojo?

Платката за развитие на Mojo е дъска за разработка, базирана на Xilinx spartan 3 FPGA. Дъската е направена от Alchitry. ПЛИС са много полезни, когато множество процеси трябва да се изпълняват едновременно.

Какво ще ви трябва?

Консумативи

Съвет за развитие на Mojo

Гербер файл

8 x 15k ома резистори (по избор*)

4 x 470 ома резистори

4 x 560 ома резистори

4 x CC седем сегментни дисплея

4 x 3 мм светодиоди

4 x тактилни превключвателя SPDT

1 x 4 -позиционен DIP превключвател за повърхностно монтиране

2 x 25 на 2 или 4 x 25 заглавки

1x 2 на 5 щифтова кутия глава

Поялник

Припой

Поток

*(ако тези резистори са пропуснати, вътрешното издърпване/издърпване трябва да бъде разрешено за съответните щифтове)

Стъпка 1: Качете Gerber в производителя на печатни платки по ваш избор

За моите платки поръчах от JLC PCB.

Единствената промяна, която направих, беше цветът, който исках да съответства на черното на Mojo.

Стъпка 2: Сглобяване на борда

При запояване винаги намирам за полезно първо да запоя най -ниските части, така че започването с резисторите е добра идея.

R5, R6, R7, R8, R9, R10, R11 и R12 са 15k ома резистори, използвани за изтегляне на превключвателите (ако използвате вътрешно издърпване/издърпване, игнорирайте това).

R1, R2, R3, R4 са 560 ома резистори, които отговарят за ограничаването на тока през 7 -сегментния дисплей.

R13, R14, R15, R16 са 470 ома резистори, които са отговорни за ограничаване на тока през 4 -те светодиода.

След това запоявайте потъващия превключвател, тактилните превключватели, светодиодите, седем сегментните дисплеи и конектора на заглавката на кутията в този ред.

Сега поставете 25 на 2 (или 2 25 на 1) в mojo, за да подравните щифтовете. Подравнете щита с щифтовете и го запоявайте на място.

Стъпка 3: Настройка на софтуера

За софтуер, отнасящ се до уебсайта на Alchitry ще ви уведоми какво ви е необходимо, за да започнете и да инсталирате Xilinx ISE. Промяната на.ucf файла, така че да знае какви пинове са свързани с това, което е важно за стартирането на вашата програма.

Ето файла.ucf, който използвам с щита:

CONFIG VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = ПЕРИОД "clk" 50 MHz ВИСОКИ 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

Не забравяйте, ако не сте инсталирали падащи резистори, за да редактирате пиновете в.ucf с

| ИЗВЪРШВАНЕ; o

| НАБИРАНЕ;

Ако искате да използвате блока за каквото и да е, връзките са както следва. Вляво е номерът на пина на блока, а вдясно е номерът на pin на mojo, който трябва да зададете във вашия.ucf:

щифт 1 = 29

щифт 2 = 51

щифт 3 = 32

щифт 4 = 41

щифт 5 = 34

щифт 6 = 35

щифт 7 = 40

щифт 8 = 33

щифт 9 = GND

щифт 10 = +V

Препоръчано:

Развитие на Drivemall Board: 5 стъпки

Развитие на Drivemall Board: В този урок ще видим основните стъпки за създаване на персонализирана Arduino платка. Използваният софтуер е KiCad за дизайна на платката и Arduino IDE за създаване и зареждане на фърмуер за платката

Ефективно развитие на Java за Raspberry Pi: 11 стъпки (със снимки)

Ефективно развитие на Java за Raspberry Pi: Тази инструкция описва много ефективен подход за разработване на Java програми за Raspberry Pi. Използвах подхода за разработване на Java възможности, вариращи от поддръжка на устройства на ниско ниво до многонишкови и мрежови програми. Приложението

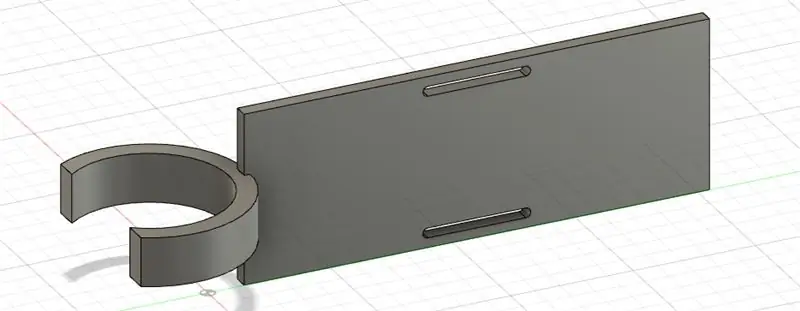

Вокален GOBO - Щит за заглушаване на звука - Вокална кабина - Вокална кутия - Рефлексионен филтър - Вокален щит: 11 стъпки

Vocal GOBO - Sound Dampener Shield - Vocal Booth - Vocal Box - Reflexion Filter - Vocalshield: Започнах да записвам повече вокали в домашното си студио и исках да получа по -добър звук и след известно проучване разбрах какво е "GOBO" беше. Бях виждал тези звукоизолиращи неща, но всъщност не осъзнавах какво са направили. Сега го правя. Намерих y

Направи си сам ESP32 борда за развитие - ESPer: 5 стъпки (със снимки)

DIY ESP32 Development Board - ESPer: Така че наскоро бях чел за много IoTs (Интернет на нещата) и повярвайте ми, просто нямах търпение да тествам едно от тези прекрасни устройства, с възможност за свързване към интернет, себе си и се хващам за работа. За щастие възможността

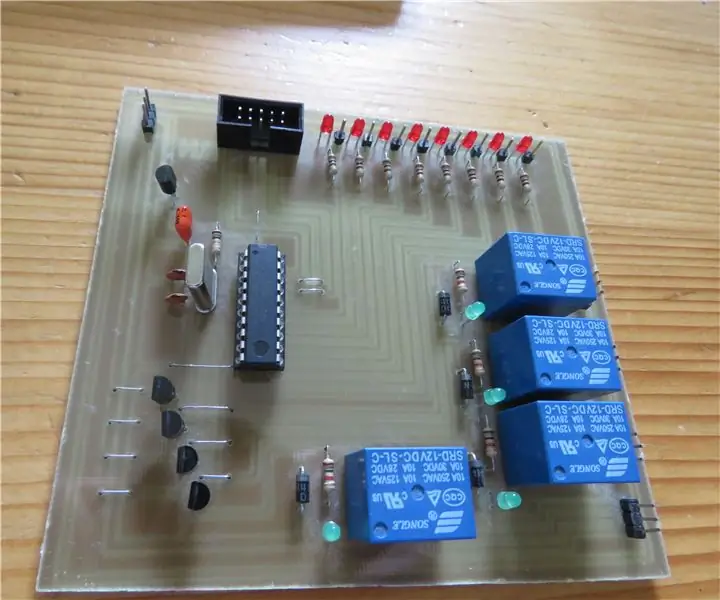

Направете своя собствена дъска за развитие с микроконтролер: 3 стъпки (със снимки)

Направете свой собствен съвет за разработка с микроконтролер: Искали ли сте някога да направите своя собствена платка за развитие с микроконтролер и не знаете как. В тази инструкция ще ви покажа как да го направите. Всичко, от което се нуждаете, са познания по електроника, проектиране на схеми и програмиране. Ако имате някакво търсене