Съдържание:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 07:49.

- Последно модифициран 2025-01-23 12:57.

В миналото съм написал ръководство за това как да се изгради компютър, базиран на Z80, и проектирах схемата да бъде възможно най-опростена, така че да може да бъде изградена възможно най-лесно. Написах и малка програма, използвайки същата идея за простота. Този дизайн работи доста добре, но не бях напълно доволен от него. Започнах с пренаписване на програма за него, която позволяваше да се програмира по време на изпълнение. Това ми позволи да тествам парчета код, без да се налага да го посвещавам на EEPROM, което от своя страна ще изисква от мен да препрограмирам EEPROM. Това не ми се стори забавна идея. Тогава започнах да мисля за пространствата на паметта. Ако исках да свържа хардуер (главно IO), парче код потенциално би могъл да надхвърли обема на паметта, наличен за системата. Не забравяйте, че дизайнът използва само долния байт на адресната шина, а след това долният бит на високия байт се използва за избор между ROM и RAM пространства. Това означаваше, че имах само 253 байта пространство за използване. Може би се питате защо 253 вместо 256. Това е така, защото моят нов код инжектира три байта данни в края на писмена програма (това ще бъде разгледано по -късно, тъй като го промених, за да работя по новия дизайн).

н

Върнах се по старите си схеми, за да видя какво друго става. Открих малък недостатък с веригата за избор на памет, която ще покрия, когато стигна там. Опростената версия: всички заявки за запис действително биха преминали, въпреки че винаги се поставят в RAM. Това вероятно не беше нещо, което си струва да се тревожи, но този път исках да го направя правилно. И с това започнах да рисувам нова схема. Двете снимки, приложени към тази страница, са преди и след действителната верига. Почистих толкова много кабелите за спагети, че не е смешно.

н

Ако сте последвали моето първоначално представяне и планирате да последвате това, ще ме мразите. Ако започвате наново, значи имате късмет. Просто вземете частите в списъка (или техния еквивалент) и следвайте.

Консумативи:

LM7805 - 5 -волтов регулатор Z80 - процесорът; мозъците на систематаAT28C64B - EEPROM. „Постоянно“съхранение на данни, използвано за фърмуера на компютъра IDT6116SA - SRAM; използва се за съхраняване на потребителски код и /или общо съхранение на данни NE555 - часовник на системата74HC374 - осмична D -ключалка с /OE; използва се като входен чип74LS273 - осмичен D -Latch с /MR; изходен чип TLC59211 - LED драйвер чип (използван така, че 74LS273 може да управлява светодиоди, тъй като сам по себе си не е в състояние да изведе текущия изход) MC14572 - Това е чип „Line Driver“, но открих, че е идеален за логиката за управление на паметта. Той има 4 инвертора и NAND и NOR порта, вградена в 74LS32 - Quad OR gateCD4001 - Quad NOR gateCD4040 - 12 Stage Ripple Counter; Изчертан, но не внедрен часовник (за работа на системата при по -бавни тактови честоти) 2 10K Ohm резистора - Един се използва във веригата на таймера 555, така че използвайте каквато стойност искате за него 4 1K Ohm резистори - Един се използва за 555 таймерна верига, така че използвайте каквото пожелаете за нея. Друг се използва за задвижване на светодиоди, така че също го променете, ако искате 8x330 омова резисторна шина 8x10K омова резисторна шина 11 светодиода - три се използват за състоянието на системата, а останалите осем са изходи. За 8 -те използвах дисплей с лентова диаграма (HDSP -4836) 4 кондензатора - два се използват LM7805; 0.22uF и 0.1uF. Единият е за таймера 555, така че използвайте това, което смятате за правилно. Последният е за нулиране при включване; 100uF2 N. O. Бутони - Единият се използва за въвеждане, другият за нулиране 8 SPST DIP превключватели - Въвеждане на данни; Използвах Piano Key styleWire. Много и много тел

н

ЗАБЕЛЕЖКА: Версията MC14572 с отвори е остаряла, но версията SMD е все още активна (дори не е в състояние „не за нов дизайн“), така че може да се наложи да закупите платка, за да можете да я използвате. Вместо MC14572 може да се използва втори 74LS32 (вижте схемата „схема за избор на памет“от предишната ible)

Стъпка 1: Бърз преглед на промените + схеми

Как да прочетете схемите: Стрелка, насочена към чип, е вход: Вход> -Стрелка, насочена от чипа, е изход: Изход <-Автобусите използват линия вместо стрелка: Bus |-

н

Повечето от чиповете са изтеглени с техните точни пиндове. Малкият спад е изтеглен върху тези чипове. Повечето чипове също имат номера на пинове и етикети. Може да са малко трудни за четене. Моливът ми ставаше тъп.

н

По отношение на електрическите връзки, оформлението на новия дизайн е почти непроменено в сравнение с оригинала. Свързах долния хапка на адреса с висок байт към паметта и след това използвах долния бит на горния байб (A12) за избор на RAM/ROM. Това означава, че ROM пространството е от 0000-00FF до 0000-0FFF. Рамковото пространство премина от 0100-01FF на 1000-1FFF. Също така замених логиката за управление на паметта за по -добър дизайн и добавих два нови светодиода за състоянието (и малко логика за лепило). Аз също съм нарисувал (но не съм свързал) верига с разделител на часовника. Той трябваше да изпълнява две функции. Очевидната функция е да разделяте тактовата честота надолу. Другата функция е за PWM (Pulse Width Modulation), тъй като 555 не генерира вълни с 50% работни цикли. Това всъщност няма значение в тази схема, но ако искате да използвате часовника за задвижване на някои светодиоди, определено ще забележите ефектите (един (набор от) светодиоди (и) ще бъде по -слаб от другия). Цялата останала схема е по същество непроменена.

Стъпка 2: Процесор, памет и контрол на паметта

Това е частта, в която читателите на предишната ми версия ме мразят. В оригиналната версия просто хвърлих части на дъската на място, което изглеждаше така, сякаш биха наложили малък проблем с свързването. Резултатът изглеждаше така, сякаш някой е изхвърлил върху него чиния със спагети и беше като „жици!“Исках да го изчистя малко, затова започнах с изрязване на всичко, с изключение на процесора, RAM и ROM. Издърпах почти цялата входна верига, изходната верига и логиката на лепилото. Почти ме нарани да го направя, но беше необходимо. Оставих всички връзки за данни непокътнати и долния байт на адресната шина. След това свързах следващите четири бита на адресната шина (A8-A11) към ROM чипа. Погрижих се да заобиколя чипа този път, за да улесня изтеглянето за препрограмиране. Също така прескачах адресните връзки до чипа на RAM.

н

След като това се отклони, сега трябваше да свържа логиката за управление на паметта. В оригиналната схема бях свързал линията на процесора /MREQ директно към /CE към двата чипа памет, след което свързах /WR към RAM /WE. Тогава логически имах процесорите /RD и /MREQ ИЛИ заедно, както и A9. По същество той беше настроен така, че всички заявки за памет активираха както RAM, така и ROM, но A9 беше използван за избор кой от чиповете /OE да бъде избран. Това беше добре и всичко, защото чиповете щяха да останат неактивни, докато не бъде направена заявка за памет и след това само един /OE ще бъде активен по време на заявка за четене. Това предотврати кръстосаните разговори, но внесе неудобен нюанс. Тъй като A9 беше използван само за определяне на чипа, който извежда данни и тъй като процесорът имаше директен достъп до щифта на RAM /WE, всички и всички заявки за запис ще преминат. Това беше добре за ROM, тъй като неговият режим на запис се инхибира чрез обвързване /WE директно към 5V захранването. В RAM обаче би било записано независимо от A9. Това означаваше, че опитът за запис на място в ROM място ще запише на същото място в RAM пространството.

н

Едно решение за това би било да пренасочим логиката за управление, така че процесорът да има директен достъп до щифтовете на чиповете /OE и /WE и след това да използва MREQ и A12, за да избере кои чипове /CE ще бъдат задвижвани. Аз отидох с тази идея, но вместо да използвам четири NOR порта и инвертор като оригиналния дизайн, намерих неудобен малък чип, който беше идеален за задачата. Трябваше да създам схема, която да използва само логическите порти, налични в чипа, но това беше достатъчно лесно. A12 подава директно в NAND порта и NOR порта. /MREQ се подава към порта NOR, а неговият комплимент се подава към порта NAND. Портът NAND се използва за задвижване /CE за RAM, а изходът NOR се инвертира и се използва за задвижване на ROM /CE. Това прави така, че /MREQ трябва да е нисък, преди да бъде избран чип и след това A12 избира кой от тях ще бъде избран. С тази настройка сега всички заявки за запис в ROM няма да направят нищо. Той също така спестява енергия, защото само един чип е активен вместо двата. Що се отнася до самия логически чип, вътре все още имаме два неизползвани инвертора. Човек ще свикне по -късно, но ще стигнем там, когато стигнем.

Стъпка 3: Светодиоди за състоянието на системата

Преди да започна този проект, се опитвах да се свържа с определена интегрална схема, но имах проблеми с нея. Не съм сигурен какво се случва, използвах светодиоден панелен монтаж, за да изследвам наоколо (един от онези възли, които имат вграден резистор). Това ми даде идея за носталгия, която се използва и до днес: светодиоди за състоянието, използвани за индикация дали паметта се чете или се записва. Той трябваше да се използва заедно с входния светодиод, който вече имах. Входният светодиод беше свързан към генератора на сигнали /WAIT, за да ни покаже, че системата е в очакване на вход (ще стигна до там, не се притеснявайте). Обмислих да добавя светодиод за индикация на IO запис, но реших, че промяната на изходните светодиоди вече ще бъде чудесен индикатор за това. Като се замисля, все още мога да го добавя. Независимо от това, намирам за полезно да знам дали паметта се чете или пише. Е, така или иначе е полезно за отстраняване на грешки в програмата. Всъщност го използвах силно като такъв, когато се опитвах да накарам програмата ми да работи: „защо пише в паметта? Още не би трябвало да го прави!"

н

За да управлявам тези светодиоди, използвах четворния NOR порта. Използвах всички порти. Само два бяха използвани за генериране на сигнали за състоянието, но чипът няма мощност за действително задвижване на светодиодите. Те са в състояние да потънат толкова много енергия, затова използвах другите две NOR порти като инвертори и свързах светодиодите като такива. Тъй като единият светодиод се използва за обозначаване на четене, а другият за запис и заявка за четене и запис няма да се появи едновременно, успях да се измъкна с използването само на един резистор за двата светодиода. Що се отнася до сигналите, които трябваше да декодирам, това също беше достатъчно лесно. Исках всички заявки за четене на памет да бъдат посочени, така че първата NOR порта имаше /MREQ и /RD на своите входове. Състоянието на писане беше малко по -сложно, но също толкова лесно. Все още използвах /MREQ като един вход, но използването на /WR като другия би причинило незначителен нюанс, който исках да избегна. Това би посочило ВСИЧКИ заявки за запис. Исках само тези, които всъщност са преминали. И така, как бих направил това? Е, помнете как съм настроил системата, така че да може да се записва само RAM? Използвах RAM /CE като друг вход към NOR порта. Това означава, че светодиодът ще светне само когато е избрана RAM и е направена заявка за запис. Що се отнася до цвета на светодиода, аз избрах оранжев като индикатор за четене (но намерих само жълти) и червен като индикатор за запис.

Стъпка 4: Вход и изход

В предишната стъпка може би сте забелязали, че вече добавих някои от останалите компоненти към дъската. Резервирах място, за да не поставя случайно проводници там, където искам компонент (по този начин ще трябва да намеря ново място за споменатия компонент). Може също да сте забелязали, че оставих входните превключватели на място и свързах към захранващата шина. Реших, че първоначалното местоположение е идеалното място и реших да поставя изходните светодиоди наблизо (горе). Вдясно от лентовия дисплей е входният фиксатор. Над това е изходното резе, а вляво от него е LED драйверът. Започнах с свързването на дисплея към драйвера, тъй като това беше най -лесно да се направи. След това свързах превключвателите към входната страна на входния фиксатор. След това свързах изходната страна на изходната ключалка към LED драйвера. Това може да изглежда като неудобна поръчка да се свържат тези кабели, но беше по причина. Входът на изходната ключалка трябваше да бъде свързан към шината за данни, както и изходът на входната резе. Идеята беше да свържа изходите на входния лост с входовете на изходния лост, което направих. Тогава всичко, което трябваше да направя, беше да свържа тази бъркотия към шината за данни. Нямаше значение къде тези връзки отидоха физически, защото всички те щяха да бъдат електрически свързани. Компютърът вече е почти свършен.

Стъпка 5: Нулиране и завършване на входа и изхода

За съжаление няма снимки за тази стъпка. Вижте предишната стъпка за снимки.

н

Може би сте забелязали на последната снимка от предишната стъпка, че имах зелен бутон и инсталиран друг логически чип. Чипът е OR порта. Два порта се използват за генериране на /WAIT сигнал. Е, човек генерира сигнала чрез OR-ing /IORQ и /RD от процесора. Изходът се подава във втората порта, където отново се връща към бутон. Бутонът извежда входа на портата високо, като по този начин извежда изхода високо. Този изход се подава към процесорите /ПИН WAIT. Докато не е натиснат, резистор държи входа нисък. Първоначално използвах 10K резистор, но LS32 всъщност извеждаше напрежение на входа. Резисторът не го спусна достатъчно ниско и трябваше да го сменя с 1K. Както и да е, идеята е, че когато се направи заявка за четене на IO, първата и втората порта ИЛИ казва на процесора да изчака. След като настроите входните превключватели на каквото искате, натискате бутона и той извежда процесора от състоянието на изчакване. Зеленият светодиод „вход“, както го нарекох в по -ранна стъпка, е свързан така, че когато щифтът /WAIT падне ниско, той светва.

н

Но още не сме приключили. Входната джапанка се нуждае от сигнал, който да я уведоми, когато въведените данни са валидни, и трябва да бъде пусната в процесора. Този часовник е активен високо. Преди просто го свързвахме с бутона. Това все още е валидна опция, но този път избрах да я сложа на същия изход като втората порта ИЛИ. Тази IC също има /OE щифт, който трябва да бъде задвижван. Ако се държеше високо, никога нямаше да вмъкне данни в шината. Ако се държеше ниско, винаги щеше да шофира автобуса. За да поправя това, просто използвах трети ИЛИ порта. Входовете са /IORQ и /RD и изходът отива директно към ключалката /OE.

н

Изходната ключалка също се нуждае от часовника за задвижване. Отново той е активен на високо ниво. В моята схема схематично нарисувах четвъртия ИЛИ порта, директно задвижвайки щифта, използвайки /IORQ и /WR. Това означаваше, че щифтът на часовника ще бъде задържан високо, докато не бъде направена заявка за запис, след което той ще падне ниско, след което отново високо. Това вероятно би било добре, защото шината за данни все още щеше да има валидни данни веднага след опита за запис, но от инженерна гледна точка беше дизайн на боклука. Не забелязах тази грешка чак след като направих последните снимки, но разкъсах тази връзка и след това подадох изхода на OR порта към един от неизползваните инвертори от логиката за управление на паметта, след което свързах изхода му към часовника. Също така оправих схемата и открих друга грешка, която направих. И аз го поправих.

н

След като всичко това най -накрая свърши, ми предстоеше много малко работа: веригата за нулиране. Добавих бутон към дъската и използвах 10K резистор, за да държа едната страна високо. Другата страна отива директно към земята. Страницата, която се държи високо, е /RESET изходът, който отива до всеки чип с щифт /RESET (процесора и изходната ключалка). За да извърша нулиране при включване, добавих кондензатор към изхода /RESET. Идеята е, че резисторът с голяма стойност би накарал относително големия кондензатор да се зарежда бавно и да задържи ниските щифтове /RESET за известно количество тактови цикли (процесорът се нуждае от четири тактови цикъла). Вероятно вече можете да се досетите каква е отрицателната страна на тази верига. Той е същият отрицателен като предишната версия, защото е същата схема. Когато бутонът е натиснат, кондензаторът по същество се късо свързва чрез бутона. Това е лошо както за капачката, така и за бутона, така че ако искате да направите вашата конструкция малко по -постоянна, може да искате да я препроектирате. Мислех за друг таймер 555, настроен в моностабилен режим. Но с това компютърната верига вече е завършена. Да. Сега има нужда от програмиране.

Стъпка 6: Програмиране

Програмирането на това нещо беше кошмар. Изградих Arduino EEPROM програмист. Не се получи. Изградих още един въз основа на чужд дизайн и кодиране. Все още не работи. Върнах се към изпитания метод за ръчно задаване на адреси и байтове с данни на ръка. По някакъв начин обърках това. Опитах отново и пак се обърках. Върнах се отново и открих, че е изключен с един байт, затова го коригирах и най -накрая проработи, слава Богу.

н

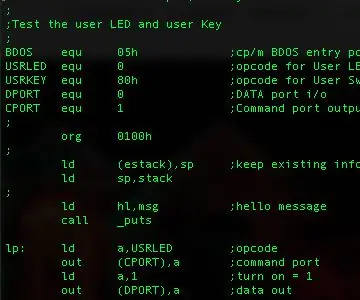

Що се отнася до действителната програма, изглежда, че е супер сложна и трудна за следване, но не е така. Всъщност е съвсем просто. Половината от тях копират числа наоколо. Другата половина се споделя между 16-битова математика, условни скокове и още повече копиране на числа наоколо. Така че нека да го разгледам и да ви кажа как работи.

н

Инициализацията просто задава някои стойности в регистъра за използване от програмата. Програмният цикъл е малко по -сложен, но не много. Първо, той приема вход към регистър А на порт 00. След това регистър Е се записва в паметта. В първите два цикъла регистърът E съдържа нежелани данни, затова се опитваме да ги запишем в последните два байта ROM пространство, защото всъщност няма да бъде записано; след това указателят на адреса (IY) се увеличава. Стойността, съхранена в D, след това се премества в E, за да бъде записана по -нататък. След това A се зарежда в D и L и E се копира в H. HL е мястото, където сравнението на стойностите се извършва чрез изваждане и проверка на ZF (нулев флаг). Първата стойност, сравнена с, се съхранява в регистри B и C. B и C се третират като един 16-битов регистър, BC. Ако стойностите са едни и същи, програмата скача направо в RAM пространството, където се предполага, че се намира потребителският код. Ако кодът в BC не съвпада, тогава HL се презарежда с началните стойности от D и E и отново се сравнява със стойността в SP по същия начин, по който е сравнен с BC. Ако е съвпадение, той има същия резултат, но три допълнителни байта се записват в паметта. Байтовете са код, който кара процесора да скочи обратно в самото начало на своята програма (софтуерно нулиране). Ако второто сравнение обаче не съвпада, програмата се придвижва до мястото, където грабва стойност от потребителя.

н

LD SP, EDBFH; exe код (добавя скок)

н

LD IY, FFEH; първоначален указател на памет за съхранение на код

н

LD BC, EDC3H; exe код (без цикъл)

н

цикъл; асемблер директива, така че не трябва да знаем къде в паметта се намира тази част

н

IN A, (00H); вземете програмни данни

н

LD (IY+00H), E; E съдържа код за съхранение

н

INC IY; преминете към следващото място в паметта

н

LD E, D; ld D в E

н

LD D, A; ld A в D

н

LD H, E; ld E в H

н

LD L, D; ld D в L

н

ИЛИ А; нулиране на флага за носене

н

SBC HL, BC; връща 0, ако е въведен exe код 2

н

JP Z, 1000H; ако е така, преминете към и изпълнете програмата

н

LD H, E; в противен случай ги опреснете до правилните стойности

н

LD L, D

н

ИЛИ А; първото изваждане може да е задало флаг за носене. Изчисти го

н

SBC HL, SP; връща 0, ако е въведен exe код 1

н

JP NZ, контур; ако не, повторете процеса (започвайки с получаване на стойност)

н

LD (IY+00H), C3H; в противен случай въведете код за скок в края на потребителската програма

н

LD (IY+01H), 00H; jump по същество действа като нулиране на софтуера

н

LD (IY+02H), 00H; това е пълно нулиране в случай, че регистрите са променени

н

JP 1000H; скочете и изпълнете потребителска програма

Препоръчано:

Преглед на Elegoo Super Started Kit Uno R3: 4 стъпки

Преглед на Elegoo Super Started Kit Uno R3: Преди няколко дни Elegoo ми изпрати този Super Starter Kit за тестване. Така че, нека видим какво има вътре. Когато отваряме този компактен калъф, можем да видим много неща. На корицата има индекс с всички компоненти. Вътре имаме благодарствена картичка с всички

Z80-mbc2 Z80 Код на флаш потребител LED: 3 стъпки

Z80-mbc2 Z80 Code Flash User LED: Това е примерна потребителска LED програма, написана на асемблер Z80 за компютъра z80-mbc2. Направих това тест и ревизия за мен, това е първата ми програма Z80 за повече от 35 години. Насладете се

KS-Garden: Общ преглед: 9 стъпки

KS-Garden: Общ преглед: KS-Garden може да се използва за напояване/обезвъздушаване/осветяване на вашата градина/оранжерийни растения в задния двор или вашите стайни растения за отглеждане на кутии (Модулен дизайн) Системата KS-Garden се състои главно от следните модули-Main системна кутия - Реле и кутия за захранване

Преглед на програмиста на JDM: 9 стъпки

Преглед на програмистите на JDM: JDM е популярен PIC програмист, защото използва сериен порт, минимум компоненти и не изисква захранване. Но там има объркване, с много варианти на програмисти в мрежата, кои от тях работят с кои PIC? В тази „инструкция

Преглед на филм и негативен филм: 8 стъпки (със снимки)

Преглед на филм и негативен филм: Открих непосредствена необходимост да мога бързо да преглеждам и записвам негативи от стари филми. Имах няколко стотици, за да подредя … Признавам, че има различни приложения за моя смартфон, но не успях да получа задоволителни резултати, затова ето това, което заснех