Съдържание:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 07:50.

- Последно модифициран 2025-01-23 12:57.

От AmCoderhttps://www.linkedin.com/in/mituFollow Още от автора:

За: Mitu Raj - Просто любител и учещ - Чип дизайнер - Софтуерен разработчик - Любител на физиката и математиката Повече за AmCoder »

## Това е най -често натисканата, популярна връзка в Google за VHDL внедряване на CORDIC ALGORITHM за генериране на синусоидална и косинусна вълна ## В момента съществуват много хардуерно ефективни алгоритми, но те не са добре известни поради доминирането на софтуерните системи над много години. CORDIC е такъв алгоритъм, който не е нищо друго освен набор от логики за изместване и добавяне, използвани за изчисляване на широк спектър от функции, включително определени тригонометрични, хиперболични, линейни и логаритмични функции. Това е алгоритъмът, използван в калкулаторите и т.н. По този начин само с помощта на прости превключватели и суматори можем да проектираме хардуер с по -малка сложност, но мощност на DSP, използвайки кабелен алгоритъм. Следователно той може да бъде проектиран като голен RTL дизайн във VHDL или Verilog, без да се използват специални единици с плаваща запетая или сложни математически IP адреси.

Стъпка 1: VHDL и Modelsim

Тук кабелният алгоритъм е реализиран с помощта на VHDL за генериране на синусоидална и косева вълна. Той може да извежда синус и косинус на входния ъгъл с голяма точност. Кодът е синтезиран на FPGA. Modelsim се използва за симулиране на дизайна и тестовия стенд.

Стъпка 2: VHDL код за проектиране и изпитателен стенд

Техниката на двоично мащабиране се използва за представяне на числа с плаваща запетая.

Моля, преминете през приложените документи, преди да кодирате.

Преминете през Симулиране на cordic_v4.vhd - Дизайнът - Входът е ъгъл в 32 бита + знаков бит; може да обработва всеки ъгъл от 0 до +/- 360 градуса с входна точност от 0,000000000233 градуса. При въвеждане -> MSB е знаковият бит, а останалите 32 бита представляват величина. -Изходът на дизайна е неговата синусова и cos стойност в 16 бита + знаков бит.ie; с прецизност 0,00001526. Моля, обърнете внимание, че изходът се показва под формата на комплимент на 2, ако съответната стойност на синус или cos е отрицателна. Симулиране на testb.vhd - Изпитателен стенд за дизайна (1) Въведете ъглите и издърпайте нулирането = '0'. След две стъпки на симулация издърпайте нулиране на „1“и „изпълнете всички“. (2) В прозореца за симулация задайте радиуса на sin и cos сигналите като десетичен и формат> Аналогов (автоматичен). (3) Намалете, за да видите формата на вълната правилно.

Стъпка 3: Прикачени файлове

(1) cordic_v4.vhd - Проектиране. (2) testb.vhd - Изпитвателен стенд за проектиране.

(3) Документ за това как да принудите ъгловите входове и да преобразувате двоичните резултати.

Актуализация: ТЕЗИ ФАЙЛОВЕ НЕ СА ОБСЕЛЕТ И НЕ СЕ ПРЕДОСТАВЯТ. МОЛЯ, ИЗПОЛЗВАЙТЕ ФАЙЛОВЕ ОТ СЛЕДВАЩАТА СТЪПКА

Стъпка 4: Mini -Cordic IP Core - 16 бита

Ограничението на горната реализация е бавна, по-ниска тактова честота на работа поради извършване на изчисления в един тактов цикъл.

- Критични пътища, разпределени в множество цикли за подобряване на производителността.- По-бърз- FPGA доказан дизайн, синтезиран до 100 Mhz часовник.- Повече площ оптимизирана в HDL, По-малък хардуер.- Добавени са сигнали за зареждане и готовност.- Единственият недостатък е по-ниската разделителна способност в сравнение с предишен. Testbench:

напълно автоматизирани от 0 до 360 градусови ъглови входове

Прикачени файлове: 1) мини кабелен главен vhdl файл 2) мини кабелен изпитателен стенд 3) Мини Cordic IP Core ръководство 4) Документ за това как да форсирате ъгли и да конвертирате резултатите

За всякакви въпроси, не се колебайте да се свържете с мен:

Миту Радж

следвайте ме:

поща: iammituraj@gmail.com

### Общо изтегляния: 325 към 01-05-2021 г. ###

### Последно редактиран код: юли-07-2020 г. ###

Препоръчано:

Самобалансиращ се робот - ПИД контрол алгоритъм: 3 стъпки

Self Balancing Robot - PID Control Algorithm: Този проект е замислен, защото имах интерес да науча повече за контролните алгоритми и как ефективно да прилагам функционални PID контури. Проектът все още е във фаза на разработка, тъй като тепърва ще бъде добавен Bluetooth модул, който ще

Настолни игри Изкуствен интелект: минимаксният алгоритъм: 8 стъпки

Изкуствен интелект за настолни игри: минимаксният алгоритъм: Чудили ли сте се как се правят компютрите, срещу които играете в шах или шашки? Е, не търсете повече от тази инструкция, защото тя ще ви покаже как да направите прост, но ефективен изкуствен интелект (AI), използвайки алгоритъма Minimax! Чрез използването на

Самобалансиращ се робот, използващ PID алгоритъм (STM MC): 9 стъпки

Самобалансиращ се робот, използващ PID алгоритъм (STM MC): Напоследък беше извършена много работа по самобалансирането на обекти. Концепцията за самобалансиране започва с балансирането на обърнато махало. Тази концепция се разпростира и върху проектирането на самолети. В този проект ние проектирахме малък мод

Tic Tac Toe на Arduino с AI (минимакс алгоритъм): 3 стъпки

Tic Tac Toe на Arduino с AI (минимакс алгоритъм): В тази инструкция ще ви покажа как да изградите игра Tic Tac Toe с AI с помощта на Arduino. Можете да играете срещу Arduino или да гледате Arduino да играе срещу себе си. Използвам алгоритъм, наречен "минимакс алгоритъм"

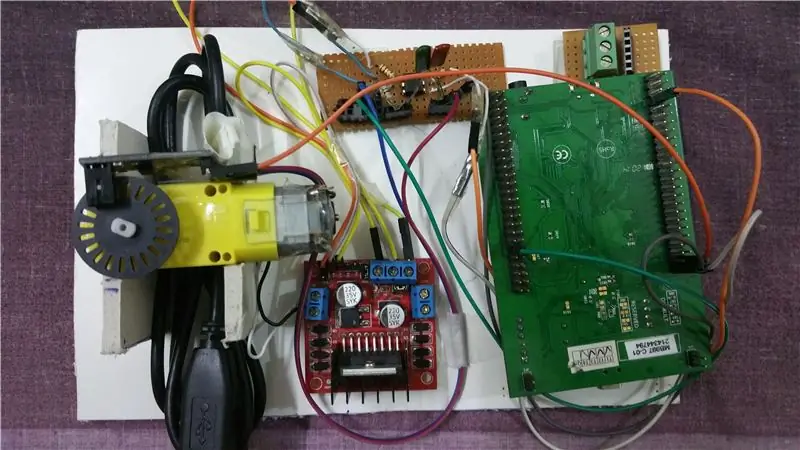

Контрол на скоростта на DC двигател с помощта на PID алгоритъм (STM32F4): 8 стъпки (със снимки)

Контрол на скоростта на DC двигател с помощта на PID алгоритъм (STM32F4): здравей на всички, Това е tahir ul haq с друг проект. Този път това е STM32F407 като MC. Това е проектът в края на семестъра. Надявам се да ви хареса. Изисква много концепции и теория, така че първо ще се заемем с него. С появата на компютрите и