Съдържание:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 07:51.

- Последно модифициран 2025-01-23 12:57.

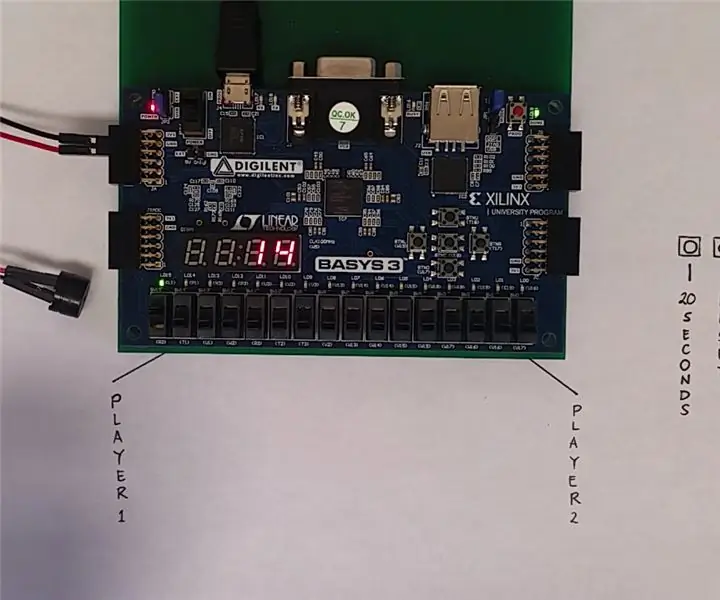

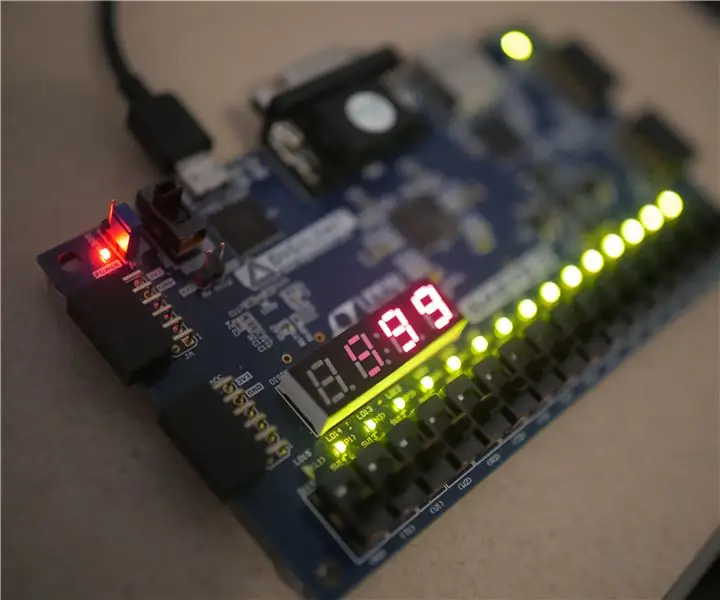

Състезателната звукова система, проектирана в този проект, работи подобно на зумерните системи, използвани в регионалните и националните състезания по научна купа. Този проект беше вдъхновен от участието ми в екипа за научни съдове на моята гимназия в продължение на три години. Винаги сме имали желанието да пресъздадем системата за заключване на зумера с таймер за 5 секунди и 20 секунди.

За да се даде някаква информация за системата на зумера, научните чаши са програмирани да въведат максимум 8 играчи (с 8 отделни зумера). След като е натиснат един зумер, зумерът на първото лице ще светне, за да посочи кой играч получава въпроса. Останалите играчи ще бъдат „заключени“, което означава, че техните зумери няма да реагират, докато модераторът не нулира системата на зумера.

След като модераторът прочете въпросите, той ще натисне бутон, за да стартира таймера за обратно броене, който ще се показва на седемсегментния дисплей. След въпрос „подхвърляне“, модераторът може да натисне десния бутон, за да започне отброяването от 5 секунди. Междувременно, след "бонус" въпрос, модераторът може да натисне левия бутон, за да започне отброяването от 20 секунди. След като таймерът достигне нула, звуков сигнал ще покаже, че на плейъра е изтекло времето.

За да нулира системата и таймера за обратно броене, модераторът може да натисне централния бутон. За да нулирате заключващия механизъм и светодиодите на плейъра, превключвателите за играч 1 и плейър 2 трябва да са на ниско ниво.

Стъпка 1: Материали

Ще ви трябва следното:

- Платка Basys3 (или еквивалентна FPGA платка)

- USB кабел Micro-B

- Високоговорител (използвах пасивен високоговорител)

- 2 проводника

- Софтуер за внедряване на FPGA (използвах Vivado)

- Конкурентна система на звуков файл

Стъпка 2: Диаграма на черна кутия

Диаграмата на черната кутия показва входовете и изходите, които ще бъдат използвани в тази система на зумера.

ВХОДИ:

player1, player2 Тези входове са свързани към два превключвателя на платката Basys3. За удобство ще се използват крайният ляв и десен превключвател.

нулиране Централният бутон ще се използва за представяне на бутона за нулиране.

count_down_20_sec Лявият бутон ще се използва за представяне на 20-секундния бутон на таймера.

count_down_5_sec Дясният бутон ще се използва за представяне на 20-секундния бутон на таймера. За да сте сигурни, че и 20-секундният, и 5-секундният таймер стартират, задръжте бутона, докато седем-сегментният дисплей покаже таймера.

CLK FPGA платката ще генерира часовник, който работи с честота 10 ns.

ИЗХОДИ:

високоговорител Изходът на високоговорителя е свързан към външен зумер или високоговорител. Ще трябва да свържете високоговорителя към JAS pmod портовете на Basys3 борда. Тази стъпка ще бъде описана по -долу.

speaker_LED Този изход е свързан към светодиод в центъра на платката и просто ще показва кога изходът на високоговорителите на FPGA е висок. Можете да използвате това за тестване на външния високоговорител. Обърнете внимание, че някои от pmod портовете може да не работят добре, така че можете да изпробвате различни и да използвате светодиода, за да проверите дали високоговорителят трябва да е включен.

СЕГМЕНТИ Този изход е свързан с осемте отделни сегмента на седем-сегментния дисплей, включително десетичната запетая.

DISP_EN Този изход е свързан към четирите анода на седем-сегментния дисплей.

player_LED Този изход е 2-пакетен сигнал, който е свързан към светодиодите над превключвателите player1 и player2. Първият играч, който обърне съответния превключвател, ще бъде обозначен със светодиода. Имайте предвид, че и двата светодиода не могат да светят едновременно.

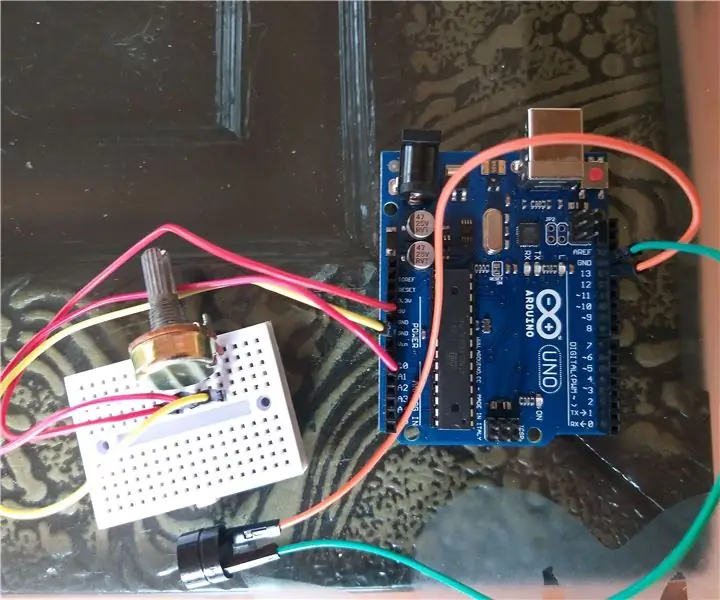

Стъпка 3: Свързване на външен високоговорител

За да свържете външния високоговорител към платката Basys3, вземете двата си проводника и ги свържете, както е посочено на горното изображение. Бялата линия свързва отрицателния извод на високоговорителя към заземяващия порт на платката. Червената линия свързва положителния извод на високоговорителя към порта JA10 pmod на платката.

Файлът с ограничения е проектиран така, че всеки порт от JA1 до JA10 трябва да работи. Някои щифтове на платката обаче не реагират, така че ако JA10 не функционира, можете да опитате другите портове.

Стъпка 4: Структурна диаграма

Изображението по -горе показва структурната диаграма на конкурентната звукова система, включваща всички компоненти, които съставляват основния модул. Техните описания са следните:

player_lockout_LED1 LED компонентът за блокиране на плейъра е машина с крайно състояние, която използва кодиране с едно горещо. Той има четири входа: player1, player2, reset и CLK. Той съдържа 2-битов пакет за изход player_LED. Входовете и изходите на компонента player_lockout_LED1 са директно свързани към идентично вписаните входове и изходи на основния модул.

buzzer_tone1 Компонентът на зумера се основава на този код, публикуван във форум

stackoverflow.com/questions/22767256/vhdl-… Въпреки това, той беше модифициран за извеждане на непрекъснат звук с честота 440 Hz (бележка A). Входът за активиране е свързан към сигнал за зумер, който е изход на компонента down_counter_FSM1.

clk_div1 Компонентът на разделителя на часовника е модифицирана версия на часовника на професор Брайън Мили, предоставен на PolyLearn. Той забавя часовника, така че изходният период е 1 секунда.

down_counter_FSM1 Броячът надолу е FSM, предназначен да отброява до нула. Двата възможни начални времена са 20 или 5, което се избира от въвеждането от потребителя. Той извежда „1“, когато таймерът е достигнал нула, за да покаже, че времето е изтекло. Този изход действа като активиране на компонента на звуковия сигнал. Броячът също извежда сигнал от 8-битов пакет, който изпраща 8-битов BCD, който се изпраща до сегментния декодер. Друг изход е counter_on, който също е свързан с валидния вход на сегментния декодер.

sseg_dec1 Компонентът за декодиране от седем сегмента е предоставен на PolyLearn и е написан от професор Брайън Мили. Той използва BCD вход, предоставен от down_counter_FSM1, и извежда десетичния еквивалент на седем-сегментния дисплей. Когато броячът е включен, тогава валидният вход е висок. Това позволява на декодера да изведе десетичния номер на седем-сегментния дисплей. Когато броячът е изключен, тогава валидният вход е нисък. Тогава седемсегментният дисплей ще показва само четири тирета.

Стъпка 5: Диаграма на крайно състояние (FSM)

Списъкът с чувствителност за машината с крайни състояния включва player1, player2, reset и часовника. Изходът на FSM е 2-битов пакет player_LED, свързан към два светодиода на платката Basys3. Машината за крайни състояния показва следните три състояния:

ST0 е стартовото състояние. В това състояние двата светодиода са изключени. FSM ще остане в това състояние, ако играч1 и играч2 са ниски. Асинхронно нулиране също задава състоянието на ST0. Когато превключвателят player1 е настроен на високо, следващото състояние ще бъде ST1. Ако превключвателят player2 е настроен на високо, следващото състояние ще бъде ST2.

ST1 е състоянието, за което светодиодът на player1 свети. FSM ще остане в това състояние за всеки вход. Това означава, че дори когато превключвателят player2 е настроен на високо веднага след превключвателя player1, той ще остане в ST1. Само асинхронното нулиране може да зададе следващото състояние на ST0.

ST2 е състоянието, за което светодиодът на player2 свети. Подобно на ST !, FSM ще остане в това състояние за всеки вход, дори когато превключвателят player1 е настроен на високо веднага след превключвателя player2 е висок. Отново само асинхронното нулиране може да зададе следващото състояние на ST0.

Препоръчано:

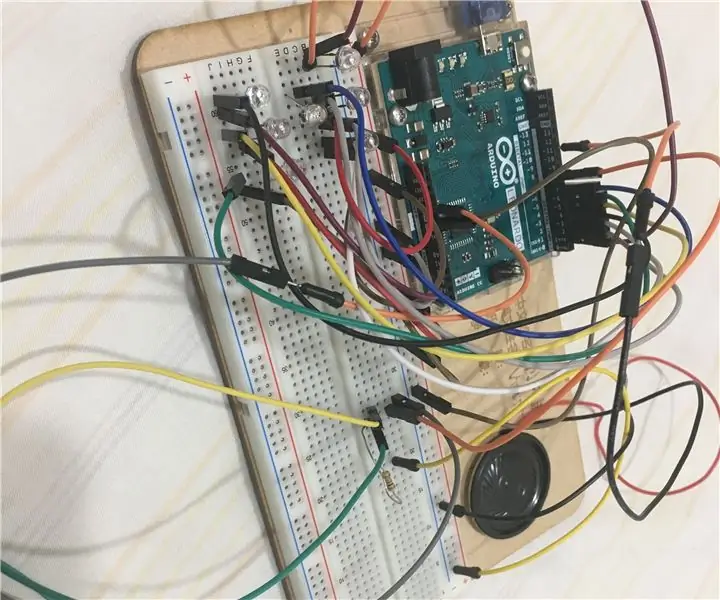

Супер Марио с помощта на зумер: 3 стъпки

Super Mario Използване на зумер: Слушането на музика отпуска ума и душата ни. Нека добавим малко музика към вашите arduino проекти, използвайки един компонент, зумер. Открих този страхотен проект с помощта на Buzzer, който свири супер песен на тема тематика, написана от Dipto Pratyaksa на инструкции. В допълнение

LED зарчета със зумер: 6 стъпки

LED зарове със зумер: Тази инструкция ще ви научи как да правите LED зарове със зумер, когато бутонът е натиснат. Оригинален източник: https://www.instructables.com/id/Easy-Arduino-LED-Dice

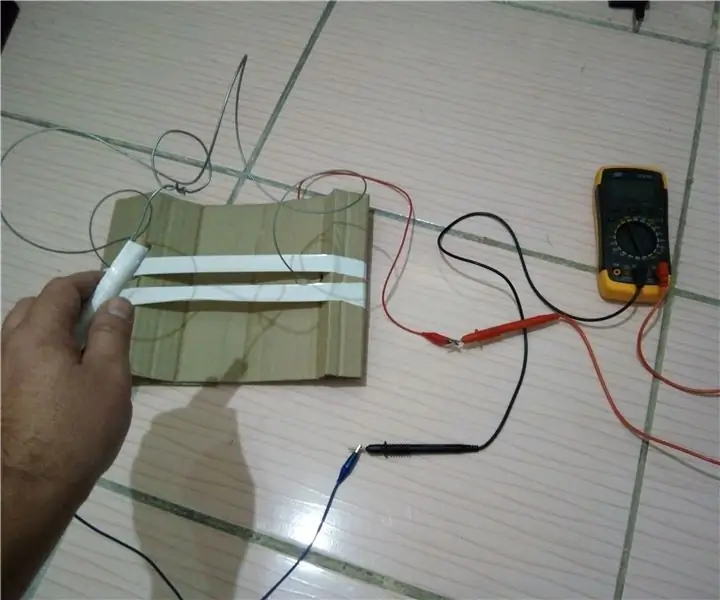

Най -лесната игра с теленен зумер! 6 стъпки

Най -лесната игра с теленен зумер досега !: Играта с теленен зумер е стара любима. Колко стабилна е ръката ви, можете ли да завършите курса, без да докосвате жицата? Идеята: Мултицетът е универсално устройство за тестване, което всеки експериментатор на електроника със собствените си ръце трябва да има в своя набор от инструменти. То ха

Честит рожден ден-зумер и бутон: 10 стъпки

Честит рожден ден-зумер и бутон: Този проект използва Arduino Uno, зумер и бутон за възпроизвеждане на песента Честит рожден ден! Когато бутонът е натиснат, зумерът възпроизвежда цялата песен на Честит рожден ден. Виждам връзката с музикалните картички за рожден ден, които децата ми обичат толкова много

Конкурентна игра срещу времето за 2 играча: 4 стъпки

Конкурентна игра срещу времето за 2 играча: Ще ви трябват: 1. Digignt Basys 3, FPGA Board (или всяка друга FPGA,) 2. Сравнително актуална версия на Vivado или друга VHDL среда3. Компютър, който може да изпълнява споменатата програма